# THE COMPLIANCE INFORMATION RESOURCE FOR ELECTRICAL ENGINEERS

# A Brief History of **ESD Testing of Products**

#### **PLUS**

Automotive High-Speed Interfaces: Future Challenges for System-Level HV ESD Protection and First-Time-Right Design

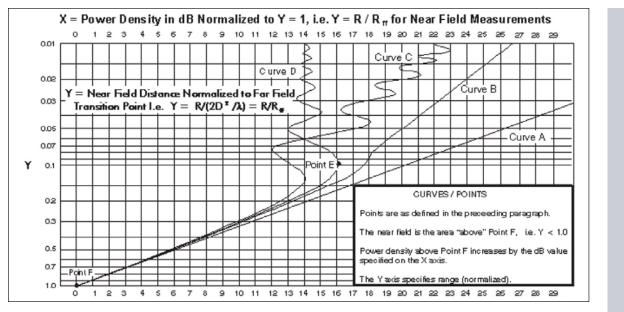

(Re)Discovering the Lost Science of Near-Field Measurements, Part 3

SPECIAL COVERAGE: EOS/ESD Symposium Preview

# Does your antenna supplier do *all* this?

|                                      | Your<br>Supplier | A.H.<br>Systems |

|--------------------------------------|------------------|-----------------|

| Design / build their own?            |                  | ~               |

| 99% in stock now?                    |                  | ~               |

| Next day delivery?                   |                  | ~               |

| Over a hundred items to choose from? |                  | ~               |

| Portable antenna kits?               |                  | 1               |

| Still working after 10 years?        |                  | ~               |

| Over 80 years of experience?         |                  | ~               |

| Personal technical support?          |                  | ~               |

| Personal Customer Service?           |                  | ~               |

| Global support network?              |                  | ~               |

A.H. Systems does *all* of this, *all* of the time because we are the EMI test Antenna Specialists. We do not build "boxes". We do not build "Systems". We do design and build the highest quality, most accurate EMI test antennas (20 Hz - 40 GHz)

It may be more convenient to buy everything from one supplier, but remember "Your test system is only as good as the antenna you put in front of it!"

Log Periodics 80 MHz - 7 GHz 13 Models

DRG Horns 170 MHz - 40 GHz 6 Models

All in one small package 20 Hz - 40 GHz

Quality

Biconicals 20 MHz - 18 GHz 7 Models

Performance

A.H. Systems

# **The Antenna Specialists**

Phone: (818)998-0223 + Fax (818)998-6892

http://www.AHSystems.com

Innovation

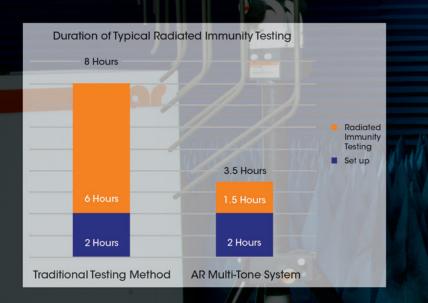

# This is How You Reduce Testing Time by More Than 50%

With regulatory adoption of multiple signal radiated immunity test methods (IEC-61000-4-3:2020, 4th edition), AR's Multi-Tone System enables you to vastly reduce your test times in accordance with automotive, commercial, and aviation EMC RI standards. Included is AR's proprietary emcware® software, offering users numerous test and calibration routines utilizing multiple signal methodology, to meet these standards.

For example, AR's Multi-Tone System can reduce the typical time to run traditional tests such as IEC 61000-4-3, ISO 11451, and ISO 11452, by over 50%. In the event of an EUT failure, margin investigation and traditional single tone testing is easily performed through AR's emcware® software.

Multiple full sweeps are often required during mitigation efforts, which is where the multiple signal approach will pay dividends.

This is a creative way to help your company be more profitable by using your assets more efficiently.

Visit us at www.arworld.us or call 215-723-8181. Talk to an applications engineer at 800.933.8181.

# The BROM

electrical engineering resource center

Visit incompliancemag.com/EERC to access your free resources today!

**TESTING FOR COEXISTENCE IN CROWDED** AND CONTESTED RF ENVIRONMENTS

white paper provided by

THE CHALLENGES OF DELIVERING LARGE ANECHOIC CHAMBERS FOR **TESTING LARGE EUTS**

white paper provided by

ELECTRONIC WARFARE AND CYBER DEFENSE OF SATELLITES (TEST METHODS)

TEMPEST SECURITY AND RISK MITIGATION

white paper provided by

white paper provided by RAYMONDEMC

USING SHIELDED ENCLOSURES

EMC 101: UNDERSTANDING **ELECTROMAGNETIC COMPATIBILITY** guide provided by

DETERMINING THE MATERIAL OF A FERRITE CORE

white paper provided by

Fair-Rite Products Corp. Your Signal Solut

| THE IMPORTANCE OF ANTENNA |

|---------------------------|

| BEAMWIDTH IN RF TESTING   |

| white paper provided by   |

In Compliance Magazine ISSN 1948-8254 (print) ISSN 1948-8262 (online) is published by

Same Page Publishing Inc. 451 King Street, #458 Littleton, MA 01460 tel: (978) 486-4684 fax: (978) 486-4691

© Copyright 2023 Same Page Publishing, Inc. all rights reserved

Contents may not be reproduced in any form without the prior consent of the publisher. While every attempt is made to provide accurate information, neither the publisher nor the authors accept any liability for errors or omissions.

| publisher/<br>editor-in-chief       | Lorie Nichols<br>lorie.nichols@incompliancemag.com<br>(978) 873-7777                                                                                                                |                                                                                                                              |  |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|

| business<br>development<br>director | Sharon Smith<br>sharon.smith@incompliancemag.com<br>(978) 873-7722                                                                                                                  |                                                                                                                              |  |

| production<br>director              | Erin C. Feeney<br>erin.feeney@incompliancemag.com<br>(978) 873-7756                                                                                                                 |                                                                                                                              |  |

| marketing<br>director               | Ashleigh O'Connor<br>ashleigh.oconnor@incompliancemag.com<br>(978) 873-7788                                                                                                         |                                                                                                                              |  |

| circulation<br>director             | Alexis Evangelous<br>alexis.evangelous@incompliancemag.com<br>(978) 486-4684                                                                                                        |                                                                                                                              |  |

| features<br>editor                  | William von Achen<br>bill.vonachen@incompliancemag.com<br>(978) 486-4684                                                                                                            |                                                                                                                              |  |

| senior<br>contributors              | Bruce Archambeault<br>bruce@brucearch.com<br>Keith Armstrong<br>keith.armstrong@<br>cherryclough.com<br>Leonard Eisner<br>Leo@EisnerSafety.com<br>Daryl Gerke<br>dgerke@emiguru.com | Ken Javor<br>ken.javor@emcompliance.com<br>Ken Ross<br>kenrossesq@gmail.com<br>Werner Schaefer<br>wernerschaefer@comcast.net |  |

| columns<br>contributors             | EMC Concepts Explained<br>Bogdan Adamczyk<br>adamczyb@gvsu.edu                                                                                                                      | Hot Topics in ESD<br>EOS/ESD Association, Inc<br>info@esda.org                                                               |  |

| advertising                         | For information about advertising contact Sharon Smith at sharon.smith@incompliancemag.com.                                                                                         |                                                                                                                              |  |

| subscriptions                       | In Compliance Magazine subscriptions are<br>free to qualified subscribers in North America.<br>Subscriptions outside North America are \$129                                        |                                                                                                                              |  |

for 12 issues. The digital edition is free. Please contact our circulation department at circulation@incompliancemag.com

# SEPTEMBER 2023 CONTENTS

Volume 15 | Number 9

#### A Brief History of Electrostatic Discharge (ESD) 8 **Testing of Electronic Products**

#### By Daniel D. Hoolihan

This updated version of an article originally published in the March 2014 issue provides details on recent and current developments in the ESD testing of electronic products.

#### Automotive High-Speed Interfaces: 14 Future Challenges for System-Level HV ESD Protection and First-Time-Right Design

#### By Sergej Bub, Markus Mergens, Andreas Hardock, Steffen Holland, and Ayk Hilbrink

This paper describes future design challenges of discrete systemlevel ESD protection (high-voltage, low-capacitance) of automotive high-speed data links such as multi-gigabit ETHERNET and SERDES/ video-links. A special focus is put on an in-depth analysis and accurate modeling of the complex ESD behavior of the Common Mode Choke (CMC).

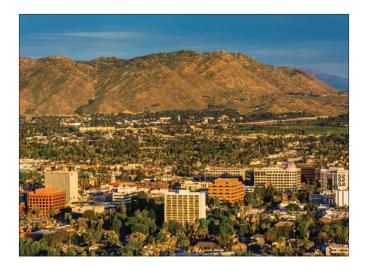

#### 45<sup>th</sup> Annual EOS/ESD Symposium 28

A preview of the Symposium taking place in Riverside, CA from September 30 through October 5, 2023.

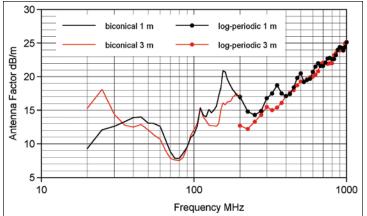

#### (Re)Discovering the Lost Science of Near-Field 32 Measurements, Part 3

#### By Ken Javor

This article is the third in a series commemorating 70 years since the advent of modern EMI testing. But this last article is itself divided into multiple parts, due to the topic's complexity. Unlike the previous two articles, which mainly tracked evolution and explained issues, this series of installments argues that we started off correctly seventy years ago, but then took the wrong fork in the road in 1967.

**Compliance News** 6

46 EMC Concepts Explained

50 Hot Topics in ESD

- 53 Product Showcase

- 54 Advertiser Index

- 54 Upcoming Events

#### FCC Proposes More Power Flexibility for FM Stations

The U.S. Federal Communications Commission (FCC) is taking steps to provide certain FM radio stations with more flexibility to increase digital power levels for their operations.

The Commission's Order and Notice of Proposed Rulemaking (NPRM) proposes to change the way FM stations determine their maximum permissible power level and, further, to give FM stations the authority to operate their digital sidebands at different power levels. According to the FCC, these changes would potentially expand the number of FM stations that can broadcast at higher digital power levels, while also giving them greater flexibility to maximize power while avoiding interference. The Commission Order and NPRM were prompted by two petitions filed with the Commission, the first in 2019 by the National Association of Broadcasters (NAB), Xperi Corporation, and National Public Radio, and the second in 2022 by the NAB and Xperi.

The FCC says that there are currently over 2000 FM stations that broadcast digitally, providing listeners with enhanced sound quality and other data through digital signals. If the FCC's Order and NPRM are adopted, the Commission says that the changes would potentially encourage more FM broadcasters to adopt digital technologies, thereby making digital broadcasts available to a greater number of listeners.

#### FCC Proposes \$20 Million Penalty for Failing to Protect Consumer Data

The U.S. Federal Communications Commission (FCC) has proposed a \$20 million fine against two affiliated wireless companies for failing to adequately secure and protect the personal data of subscribers. According to a Notice of Apparent Liability for Forfeiture, the companies, Q Link Wireless LLC, and Hello Mobile Telecom LLC, routinely relied on readily available biographical and account information to authenticate

online customers. Customers authenticated in this way were then given access to "customer proprietary network information" (CPNI), placing customer information at risk of unauthorized access and disclosure.

#### FDA Updates List of Recognized Standards

The U.S. Food and Drug Administration (FDA) has updated its list of recognized international and national standards that can be used to demonstrate compliance with certain requirements for premarket review and authorization of medical devices. In a Notice published in the *Federal Register*, the agency announced 29 additions and 25 modifications to the list of FDA Recognized Consensus Standards. Notable among the new standards added to the list are ISO 60601-2-35, which details requirements for the safety and performance of heating devices, and IEC 810001-5-1, which addresses the security in the product lifecycle of health software and health IT systems. Also newly added to the list of recognized standards is ISO/TS 11137-4, which addresses process control on the use of radiation in the sterilization of healthcare products.

#### FCC Backs U.S. Cybersecurity Labeling Program for Smart Devices

The U.S. Federal Communications Commission (FCC) is reportedly moving ahead with plans to develop and implement a voluntary labeling program for connected smart devices that meet rigorous cybersecurity requirements.

In remarks presented at the White House in Washington, DC, FCC Chair Jessica Rosenworcel announced that she has presented to the Commission a proposal to launch the first-ever voluntary "U.S. Cyber Trust Mark" Program. The proposed program, which would qualify connected smart devices to bear the Cyber Trust Mark, would help consumers to identify secure products while also creating incentives for device manufacturers to meet rigorous cybersecurity standards.

"Just like the 'Energy Star' logo helps consumers know what devices are energy efficient, the Cyber Trust Mark will help consumers make more informed decisions about device privacy and security," Rosenworcel noted. "What's more, because we know devices and services are not static, we are proposing that along with the mark we will have a QR code that provides up-to-date information on that device."

Rosenworcel said that the proposed Cyber Trust Mark Program is based on extensive work by the U.S. National Institute of Standards and Technology (NIST) to develop criteria for cyber secure devices.

#### Unintended Satellite Emissions May Interfere with Radio Astronomy

In the 21st century, we rely more and more on earth-orbiting satellites to support communications technologies here on the ground. But scientists are now discovering a potential problem with satellite emissions that may warrant attention.

A recent article posted to the *Sky & Telescope* website provides an overview of recent research conducted by space experts at the Max-Planck Institute for Radio Astronomy in Germany and other institutions associated with the Square Kilometre Array Observatory. According to the article, researchers looked for radio signals from satellites in SpaceX's Starlink fleet. Of the 68 satellites they observed, they detected radio emissions from 47 satellites in the 110-188 MHz frequency spectrum, well below the 10.7-12.7 GHz signals used for downlink communication signals from the satellites. The leaked signals detected by the researchers are stronger than those allowed under current regulatory limits, but current limits apply only to intentional emissions, with no stated limits applicable to unintentional emissions.

The obvious challenge for researchers, according to the article, is the additional time required to eliminate from their research data that may have been contaminated by the unintentional emissions. But the potentially larger issue is that weaker signals that hide under the underlying noise might lead to incorrect research assumptions and results.

Researchers say that the unintended emissions problem is not limited to Starlink satellites, but instead is a potential issue for each of thousands of the satellites that operate in earth orbits. This significantly raises the risk that the operation of ground-based radio telescopes will be impacted.

The solution, according to the researchers, is for scientists and industry to actively work together to develop effective mitigation strategies, while also campaigning for regulatory changes that address the root cause of the problem.

# A BRIEF HISTORY OF ELECTROSTATIC DISCHARGE (ESD) TESTING OF ELECTRONIC PRODUCTS

Revisited and Revised as of 2023

Daniel D. Hoolihan is the founder and principal of Hoolihan EMC Consulting. He is the Immediate Past-Chair of the American National Standards Committee C63 on EMC. He is also a past president of the IEEE's EMC Society and the current Chair of the History Committee of the Society's Board of Directors.

Hoolihan is also an assessor for the NIST NVLAP EMC and Telecom Laboratory Accreditation program. He can be reached at danhoolihanemc@aol.com.

#### By Daniel D. Hoolihan

ith the inventions of the transistor in 1947 and the integrated circuit in 1958, and the utilization of these major solid-state breakthroughs in the development of computers and other electronic devices, industry began to worry about designing components and end-products that could survive the impact of electrostatic discharges to chips, printed circuit boards, and final packaged-products. The 1960s and 1970s saw individual companies developing their own ESD test values and laboratory test techniques. The International Electrotechnical Commission (IEC), which is closely related to the International Standards Organization (ISO), got involved in the 1980s with the release of IEC 801-2 in 1984 on ESD limits and susceptibility test methods. Since the late 1980s, most electronic companies test their end-products for ESD immunity in accordance with the specifications found in IEC 801-2 and its follow-on standard, IEC 61000-4-2.

#### IN THE BEGINNING

The electrostatic discharge (ESD) phenomena have been known since the Greek civilization was dominant thousands of years ago. Experiments with glass rods and cloth material produced ESD sparks. And people in colder climates were very familiar with the ESD effect due to a low-relative humidity environment inside a building or house. They frequently experienced an ESD event as they walked across a carpet in the winter season.

As electronic components changed from electronic tubes to solid-state electronics in the 1950s, companies became concerned with the potential for physical damage to solid-state electronic components, interference to, and interruption of normal operation of electronic equipment. This article primarily addresses the latter of those two situations, that is, the interruption effects of ESD on packaged electronic equipment.

#### THE 1960S AND 1970S

Most electronic companies in the 1960s and 1970s were aware of and concerned about ESD. The companies tended to have proprietary standards and test methods on ESD and were not interested in exchanging information with their competitors on ESD.

The Human Body Discharge model was commonly used by companies to test products with an ESD tester. The capacitance of a human being was estimated to be in the 100 to 250 picofarad range depending on the size of the person and the length and shape of the human's shoes. A common discharge value for early standards was 5000 volts. The discharge resistance was often taken as 500 ohms, the resistance of the human finger. The discharge was an air-gap discharge that closely simulated the actual ESD phenomena.

There were some companies that were using a contact discharge approach to ESD where the ESD tester was in physical (metal-to-metal) contact with the electronic equipment. The contact discharge was a more repeatable method than the air discharge method. Oftentimes, thousands of contact discharges were used to simulate the effects of one event, and statistical analysis was used to determine pass or fail criteria for the ESD test.

The common joke among EMC consultants in the 1970s was about the correct magnitude of the ESD discharge. In most cases, companies started at a recommended 5 kilovolts amplitude. Then, when all products could pass that level, consultants would increase their recommendation to 7500 volts amplitude so they could continue to consult with the customer and improve the design of the product.

#### **KANGAROO LEATHER**

A United States computer company in the 1970s began experimenting with ESD relative to its computers and computer peripherals. A Van de Graaf generator, some high-voltage sources, and a green nylon carpet were all tried as potential ESD generators. After experimenting with the three options, it was decided to go with the standard green nylon carpet concept. A number of volunteers were organized and asked to shuffle their feet on the carpet in a controlled humidity environment while holding onto a scientific electrostatic voltmeter. Again, in most cases, at relative humidity levels of 10% and greater, about 5 to 7.5 kilovolts was the maximum value measured on the human subjects.

One product made by the computer company had a wide distribution in Australia, and it had ESD problems while the same product shipped to other countries had no ESD problems. An engineer from the company who worked with the Australian customers visited the EMC lab and discussed the issue with the EMC lab engineers. The engineers took the Australian engineer into the controlled environment and asked him to shuffle his feet while connected to the electrostatic voltmeter. Much to the EMC lab engineers' surprise, the voltmeter registered 18000 volts!

After some discussions with the Australian native, it was discerned that he had normal clothing on his body with the exception of his shoes which were made of kangaroo leather. Needless to say, the lab made that fact known while in parallel developing an engineering fix to its product to allow it to pass 18 kilovolts.

#### **THE 1980S**

The 1980s saw the release of the IBM Personal Computer in 1981, which legitimized the PC market and led the computer industry to develop desksupported computers (desktop, laptop, etc.) and similar desk-based electronic products for the manufacturers of medical equipment, laboratory equipment, etc.) based on international standards to help ensure satisfactory ESD product performance.

#### IEC 801-2 - 1984

The first edition of International Electrotechnical Commission (IEC) Publication 801-2 was released in 1984. It was titled "Electromagnetic Compatibility for Industrial-Process Measurement and Control Equipment – Part 2: Electrostatic Discharge Requirements."

#### The standard carefully pointed out in a note that:

"From the technical point of view, the more precise term for this phenomenon would be 'static electricity discharge.' However, the term 'electrostatic discharge' (ESD) is widely used in the technical world and in technical literature. Therefore, it has been decided to retain the term ESD in the title."

The characteristics of the ESD generator in the 1984 edition were: energy storage capacitor - 150 pF +/- 10%; discharge resistor - 150 ohms +/- 5%; and an output voltage of 2 kV to 16.5 kV (the output voltage was a positive voltage only!). The rise-time of the discharge current was 5 ns +/- 30% at 4 kV and the pulse width was approximately 30 ns +/- 30%. The test was an air-discharge test only.

The 1984 edition did have a requirement for discharging to the earth reference plane to simulate discharges to objects in the vicinity of the equipment under test (EUT).

Figure 5 of IEC 801-2 illustrated the "test set-up for table-top-mounted equipment, laboratory tests." There was no "ground reference plane" on the floor; instead, the "earth reference plane" was on top of the table and grounded to a mains terminal (earth connection) via a cable. The insulating support between the EUT and the earth reference plane was 10 cm (4 inches) thick.

#### SECOND EDITION OF IEC 801-2 - 1991

The second edition of IEC 801-2 was released in 1991. One of the major changes in the standard was that the contact discharge was the preferred test method and not the air discharge method.

The energy storage capacitor remained at 150 pF but the discharge changed to 330 ohms plus or minus 10%. The output voltage was increased to 8 kilovolts for contact discharge and 15 kilovolts for air discharge (both positive and negative pulses were mandated!). The rise-time at 4 kilovolts had decreased to 0.7 to 1 nanosecond. The values of the parameters of the discharge current had to be verified with a 1 GHz oscilloscope. The grounding cables from the newly

#### EXODUS Above Above

with our frequency

& power capabilities

AMP4066A-1LC, 26.5-40GHz, 100W

**Exodus** provides "Industry Firsts" covering these frequency ranges in all SSPA:

1.0-18.0GHz, 100w, 200W, 300W, 500W... 1.0-40.0GHz, as well and for the 18.0-40,0GHz range 40W, 100W, 200W

# NO OTHER COMPANY CAN DO THIS ANYWHERE!!!

3674 E. Sunset Road, Suite 100, Las Vegas, Nevada 89120 702-534-6564 • www.exoduscomm.com • sales@exoduscomm.com

COMMUNICAT

implemented vertical coupling plane (VCP) and its complement, the horizontal coupling plane (HCP) to the ground reference plane, had 470-kiloohm resistors located at each end of the cables.

#### **VERTICAL COUPLING PLANE (VCP)**

A VCP is called out in modern-day ESD standards. The basis for the VCP is a metal filing cabinet (usually four-drawer) that was commonplace in the offices of industry. The ESD charge simulated an employee walking across a floor, touching the handle of the metal filing cabinet, and discharging ESD energy to the cabinet, which would then re-radiate the field from the side of the cabinet.

#### HORIZONTAL COUPLING PLANE (HCP)

The development of the HCP started with a wellknown cash-register company in the 1970s. At that time, they had an air-discharge ESD gun which was used for their product development testing. The EMC engineers very cleverly developed an all-plastic cash register and the ESD gun would not discharge to the cash register. Therefore, by definition, the product passed the ESD test.

The all-plastic cash register went into production and out into the real world with real customers. One of the first buyers of the all-plastic cash register was a fast-food restaurant that used an all-metal countertop to separate the customers from the employee/kitchen area. When winter came, the customers would enter the restaurant and discharge an ESD event to the 3-meter-long metal countertop. The countertop would then re-radiate the ESD energy, affecting the allplastic cash register's electronics and immediately opening the cash drawer. The fast-food restaurant company was not pleased and returned the all-plastic cash registers to the manufacturer.

The EMC engineers went back to work. They placed a metal ground plane under the all-plastic cash register and discharged to the metal ground plane (now known as the HCP) to simulate the real-life experience. They eventually came up with design fixes that allowed the all-plastic register to pass the ESD test.

#### FIRST EDITION OF IEC 1000-4-2

The follow-on standard to IEC 801-2-1991 was IEC 1000-4-2 – *International Standard on EMC* –

Part 4: Testing and Measurement Techniques – Section 2: Electrostatic Discharge Immunity Test – Basic EMC Publication, which was released in 1995.

(Note: European regulators put a "6" in front of the "1000-4-2" and the International Community followed suit in the 1996 timeframe. So all the "IEC 1000" series standards became the "IEC 61000" series.)

The parameters of the ESD generator remained the same as those found in the 1991 IEC 801-2 standard; that is, the energy storage capacitor was 150 pF, the discharge resistance was 330 ohms, and the output voltage of 8 kV for contact discharge and 15 kV for air discharge. The polarity of the output voltages was both positive and negative.

Figure 5 ("Example of test set-up for table-top equipment, laboratory tests") from the 1995 version of IEC 1000-4-2 showed a horizontal coupling plane on the tabletop that was larger than the earth reference plane on top of the table in the1984 standard, a vertical coupling plane (unmentioned in the 1984 standard), a ground reference plane on the floor, and grounding cables between the HCP and VCP and the ground reference plane (with 470 kiloohm resistors on both ends of the grounding cables.) Note that the insulating support between the EUT and the horizontal coupling plane was only 0.5 mm thick, reduced from 10 cm (100 mm) thick in the 1984 edition.

Released in 1998, Amendment 1 of IEC 61000-4-2 (1000-4-2) modified the language in Figure 5 to read "Example of test set-up for table-top equipment tests."

Released in 2000, Amendment 2 of IEC 61000-4-2 (1000-4-2) added a new clause (7.1.3) – "Test Method for Ungrounded Equipment," which included 7.1.3.1 – "Table-Top Equipment," and 7.1.3.2 – "Floor-Standing Equipment." It also replaced three paragraphs in 8.3.1 ("Direct Application of Discharges to the EUT"). Finally, it replaced Clause 9 with a new Clause 9, and it added Clause 10 – "Test Report."

#### SECOND EDITION OF IEC 61000-4-2

The second edition of IEC 61000-4-2 was released in 2008 and it nullified and replaced the first edition published in 1995, as well as Amendment 1 (1998) and Amendment 2 (2000). The key parameters of the Electrostatic discharge testing has evolved from a company-based reliability test in the 1960s and 1970s to a performance test on electronic products in the 2023 timeframe.

ESD generator remained constant at 150 pF for the energy storage capacitor and the discharge resistance was set at 330 ohms. The output voltage for contact discharge remained constant at the highest value of 8 kilovolts and the air discharge at 15 kilovolts. The amplitudes were quoted in both the negative and positive polarities.

#### AMERICAN NATIONAL STANDARDS COMMITTEE (ANSC) C63 ON EMC (C63 COMMITTEE)

The C63 Committee produced a guide to electrostatic discharge testing in 2016, American National Standards Institute (ANSI) - C63.16-2016 titled "American National Standard Guide for Electrostatic Discharge Test Methodologies and Acceptance Criteria for Electronic Equipment."

#### The Introduction to the Guide states:

"This guide is intended to provide supplemental information for performing electrostatic discharge (ESD) testing to other established ESD standards by including information and test procedures that are not covered in those documents. It strives to improve product quality through proper operation in actual equipment installations. The suggestions provided herein should not be construed as mandatory and they should not be applied arbitrarily to all types of electronic equipment. <u>Performance or acceptance test levels are not given in</u> <u>this guide</u>. The specification of performance or acceptance levels for any particular type of electronic equipment remains the responsibility of the manufacturer and the users of the particular equipment."

#### The Guide's Scope is:

"This guide provides electrostatic discharge (ESD) test considerations that a manufacturer should use in assessing the expected ESD effects on products in a wide range of environments and customer use. The focus is well beyond that used to simply show that a product complies with a local, regional, or international standard or regulation. The following are included: charged peripheral testing, connector pin testing, and details on the use of ESD simulators. Finally, suggestions for assuring the safety of those who apply the ESD discharge are provided. The annexes include information on test method selection and more background on air and contact discharge for those who want to further understand the differences in these methods. This guide is not applicable to manufacturing, service, or maintenance of equipment. Personnel who perform these activities should be trained to avoid ESD effects or damage to the equipment. In summary, this guide has test techniques beyond those that are commonly used (e.g., IEC 61000-4-2), and hence it can be a significant tool for increasing the immunity of products to ESD events."

#### SUMMARY

Electrostatic discharge testing has evolved from a company-based reliability test in the 1960s and 1970s to a performance test on electronic products in the 2023 timeframe. The requirement is for electronic products to operate successfully when subjected to ESD phenomena representing the real-world environment as simulated in an electromagnetic compatibility testing laboratory. The emphasis has switched from the susceptibility of equipment to quoting how immune a product is to air-discharge and contact discharges from a portable ESD tester whose output is compliant with the latest international standard criteria.

The next version of IEC 61000-4-2 is currently under development by the IEC. The third edition of the standard is expected to be published around April 2025.

A valuable Guide was published in 2016 by the ANSC C63 Committee on EMC to aid engineers in understanding and using the universally recognized IEC standard on ESD (61000-4-2).

### AUTOMOTIVE HIGH-SPEED INTERFACES: FUTURE CHALLENGES FOR SYSTEM-LEVEL HV ESD PROTECTION AND FIRST-TIME-RIGHT DESIGN

Sergej Bub, the lead author of this paper, is a System Level ESD expert at Nexperia Germany GmbH in Hamburg. He works in the development department in the area of ESD protection and filtering, focusing on modeling and simulation of high-speed application systems and discrete ESD protection components, covering automotive, mobile, and computing areas. Sergej can be reached at sergej.bub@nexperia.com.

#### By Sergej Bub, Markus Mergens, Andreas Hardock, Steffen Holland, and Ayk Hilbrink

**Editor's Note:** The paper on which this article is based was originally presented at the 43<sup>rd</sup> Annual EOS/ESD Symposium in October 2021. It was subsequently awarded the 2021 Symposium Outstanding Paper at the 44<sup>th</sup> Annual EOS/ESD Symposium in September 2022. It is reprinted here with the gracious permission of the EOS/ESD Association, Inc.

#### INTRODUCTION

The automotive industry is experiencing a revolutionary transformation towards electrification, autonomous driving, as well as more connectivity and information. Thus, in-vehicle-network architecture is changing with an exploding amount of data cars need to process at high-speed. For example, infotainment content is rapidly increasing with an average of 20 cameras and 15 displays per vehicle. In addition, the new zonal architecture requires a new IP based protocol. Here, the automotive ethernet plays a key role for the links with data rates up to 1 Gbit/s today and multi-Gbit/s in the future. The so-called Open Alliance Committee defines a standard for those links in EHTERNET 100/1000BASE-T1, especially for the ESD protection device [1].

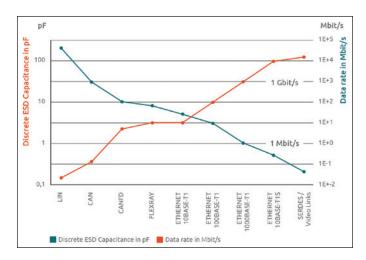

Figure 1 depicts the general trend (blue curve) of invehicle networks data-rates for different automotive protocols from the legacy LIN, CAN, FLEXRAY to the advanced protocols of ETHERNET up to SERDES. The orange curve shows the corresponding maximum of permissible parasitic capacitance of the discrete ESD component at the data line (partly from author's experience).

Significant ESD challenges result from the OPEN Alliance Ethernet specification [1], requiring the ESD protection device being robust for minimum of 1000 discharges at 15 kV ESD IEC 61000-4-2 pulse. At the same time, the discrete ESD capacitance is demanded to be continuously reduced for future highspeed protocols even below levels of 0.5 pF to ensure RF signal integrity. These two conflicting trends can only be met with highly advanced, discrete ESD architectures while on-chip ESD in the IC transceiver often does not suffice those requirements anymore.

In addition, the specification [1] recommends placing the external ESD component close to the connector, see Figure 3, instead of a position directly at the IC, i.e., behind the decoupling capacitors. The intention of this modification was to safeguard the overall system including all discrete components located in the signal path and to fulfill the EMC immunity requirements such as Direct Power Injection (DPI) acc. to IEC 62132-4 [2]. As a consequence of this placement, the new topology demands a more challenging high-voltage ESD specification with a high trigger  $V_{t1}$  > 100 V and high holding voltage  $V_{hold}$  > 28 V to prevent triggering of the ESD protection device during normal operation and disturbances. For earlier Ethernet links, those high-voltage values were not required since a low-voltage discrete ESD component protection was sufficient behind the decoupling cap directly at the IC.

Figure 1: Automotive communication protocols with increased data rates from 20 kBit/s (LIN) to multi-Gbit (ETHERNET, Serdes). Impact on maximum permissible capacitance to be added by discrete ESD component to the high-speed data lines.

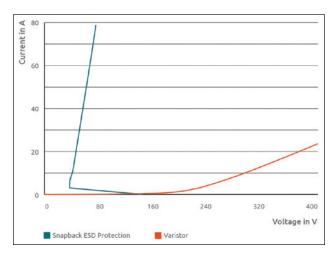

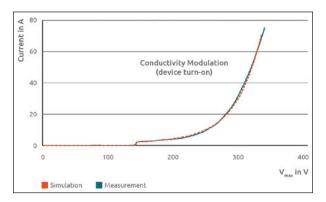

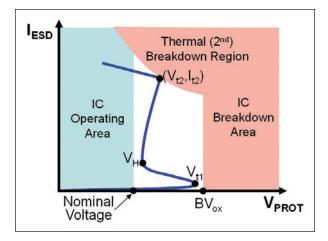

For those modern links described above, a siliconbased discrete ESD component (snapback-type) with  $V_t \approx 140 \text{ V}, V_{hold} \approx 35 \text{ V}$ , and  $R_{dyn} \approx 0.1 \Omega$  can be used, see Figure 2.

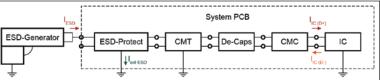

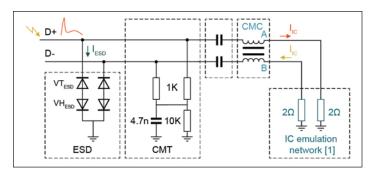

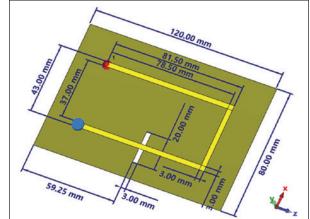

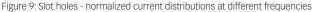

To measure the residual and potentially damaging current into a PHY (i.e., IC) for a systemlevel ESD event, a special PCB test network is recommended by OPEN Alliance 100BASE-T1 and 1000BASE-T1 applications [1]. This network is shown in a block diagram in Figure 3 with the discrete ESD component at the connector, a common mode termination (CMT), a decoupling capacitors, a common mode choke (CMC), and PHY (transceiver IC), more detailed in Figure 16.

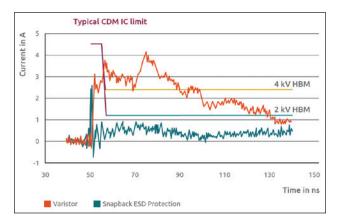

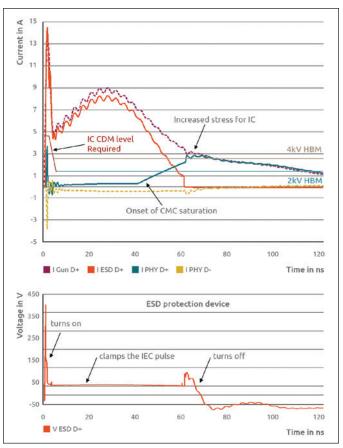

Figure 4 displays an example for a measured residual IC current transient  $I_{IC}$  for 6 kV-ESD generator stress, acc. to [2], for two different protection device types, such as snapback and varistor, see TLP I-V characteristic in Figure 2. Apparently, the IC current can be safely limited applying the advanced snapback-type ESD protection device while the varistor admits an approximately 6x higher peak current into the IC due to the relatively high ESD voltage clamping.

This level violates even a 4 kV-HBM limit. It should be noted that the initial current spike demands a certain Charged Device Model (CDM) robustness-level from the transceiver IC for both cases, as discussed below in more detail. Apparently, limiting the systems ESD voltage exposure with appropriate discrete snapback clamps can be important for protecting advanced automotive high-speed interfaces.

Following system-level design challenges are addressed in this paper:

• CMC filters in the data-line play an important role also for ESD protection of the system IC as will be discussed in detail by measurement and simulation. Moreover, the CMC trend for smaller inductance L for higher data transmission may lead to a reduced ESD blocking capability of the CMC and this to a more critical ESD exposure to the entire system, as investigated by the transient SEED simulations Therefore, the ESD behavior of different CMCs is studied in detail and compared for the first time as well as its impact on systemlevel ESD protection .

• ESD discrete protection parameters become more challenging, since there is a trend towards an

Figure 2: Transmission Line Pulse (TLP) I-V curve of discrete ESD devices for an Ethernet 1000BASE-T1 application: State-of-the-art silicon- based snapback device vs. varistor.

Figure 3: Equivalent circuit block diagram of system SEED model for the ESD current measurement.

Figure 4: 6 kV ESD generator on ETHERNET test board: comparison of residual stress current into PHY (IC) for two discrete ESD protection types: siliconbased snapback device vs. varistor, see Figure 2. IC ESD limits: 2 and 4 kV as derived with respect to the discharge resistance of 1.5 k $\Omega$  in the Human Body Model (HBM) and typical CDM peak current IC robustness. increased holding voltage, e.g., from 35 to 60 V or higher to comply for instance with a 48 V board nets and a robust system operation. This results in a larger ESD voltage stress for the system and thus higher currents into the RF-IO pins. In this paper, this behavior is investigated by system-level transient simulations based on the 1000BASE-T1 application.

#### **ESD BEHAVIOR AND MODELING**

This section outlines the ESD behavior and modeling of the relevant Ethernet system components for SEED with a special focus on CMC RF filter.

#### **ESD Pulse Generator**

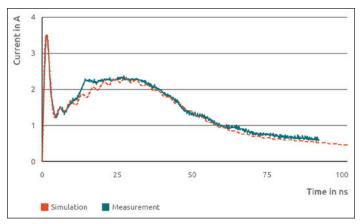

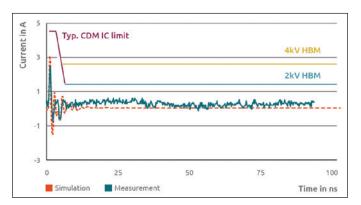

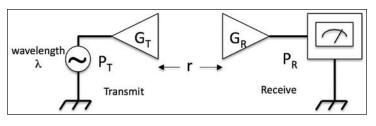

A NoiseKen ESD generator was used for contact discharge of 1 kV into a 2  $\Omega$  Pellegrini target delivering a reference current waveform for model parameter extraction. Figure 5 shows a good fit between measurement and simulation [4].

Figure 5: Current waveform of an ESD generator IEC 61000-4-2 [3] at 1 kV contact discharge through a 2  $\Omega$  reference target: simulation vs. measurement.

# Why An ESD Flooring System?

A flooring installation is only as strong as its weakest component. It could be floor prep or installation. The haphazard use of ESD footwear. Or incompatible seating.

Any of these factors can compromise the integrity of your ESD-control program.

For optimal results, think of ESD flooring as an interdependent system. Of compatible, ANSI-certified parts.

Call us: 617-923-2000

#### **ESD** Protection

To predict both the dynamic (ref. first IEC current peak) and quasi-static (ref. second IEC current peak) system ESD performance, a precise behavioral model of the external ESD protection was created [4].

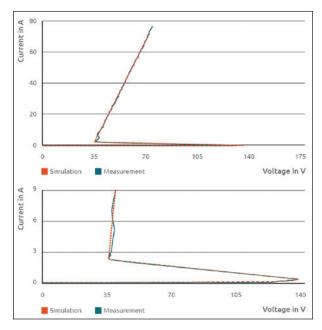

Figure 6 shows an excellent match of the quasi-static measured TLP I-V with the simulation.

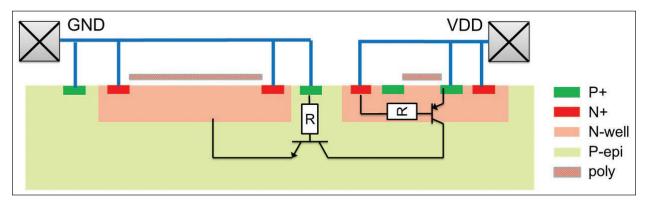

As already described in Section I, the capacitance constraints for discrete ESD protection at multi-Gbit/s data links shown in Fig. 1 requires minimizing the overall junction capacitance typically using lowlydoped Epi regions in these high-voltage transistors.

As a result, the turn-on time caused by conductivity modulation of the high-resistive region creates a relatively large transient trigger voltage overshoot, see Figure 7. Consequently, for a high simulation accuracy an adequate modeling of this transient ESD behavior is crucial and demonstrated by a comparison to the corresponding simulation.

Here, a behavioral dynamic model was tuned for accurate transient trigger voltage simulations making use of fast rise-time TLP curves [4].

Figure 6: Discrete ESD protection (high-voltage snapback-type) TLP I-V characteristic in simulation vs. measurement.

#### **Common Mode Choke**

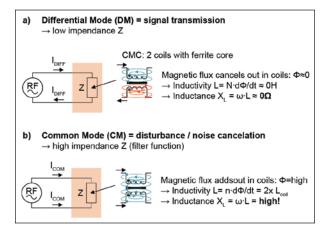

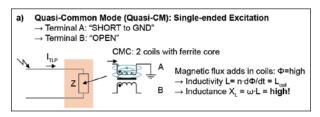

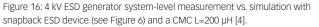

The CMC plays an important role not only to ensure RF signal integrity (SI) of the Ethernet application, but also to guarantee a certain systemlevel ESD robustness, as discussed in detail in this paper. The CMC architecture is in principle the same as in a transformer and based on two coils coupled thru a ferrite core, see Figure 8. Each coil connects thru the CMC terminals to one of the differential data-lines. During signal transmittance which is done simultaneously over both data-lines in a differential mode (DM), see Figure 8 a), the CMC appears to be in a low impedance state letting the signal pass through with minimal losses. This is because in the DM, roughly equal currents flow through both data lines and coils in opposite directions. The opposite current polarity creates a cancelation of related magnetic fluxes and a resulting minimum coil inductivity.

Figure 7: TLP I-Vmax characteristic in simulation vs. measurement showing the dynamic trigger voltage as a function of TLP current amplitude.

Figure 8: Principle of CMC modes for differential RF signal with low impedance (a) and common mode noise with high impedance (b).

The noise which is accommodating the signal on both data-lines corresponds to a common mode (CM) conduction, see Figure 8 b) i.e., non-differential. It will be suppressed by the CMC due to a high impedance. This ensures the overall RF signal integrity. Under the CM condition, both coil currents have the same direction while magnetic flux can add resulting in a maximum overall inductivity.

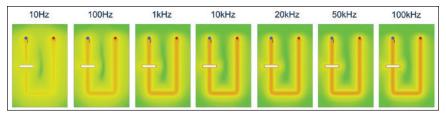

#### CMC operation during ESD

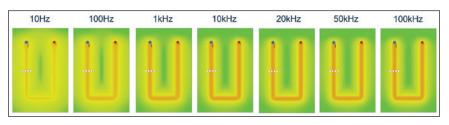

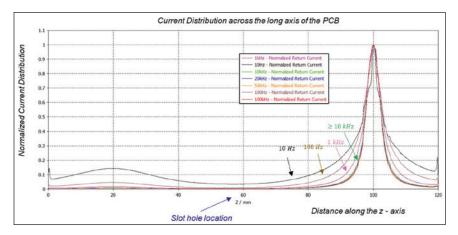

In the ESD stress case of one data line only, however, we can consider a third CMC operating mode. Here, the ESD pulse propagates only through one of the data-lines and thus coils, representing the so called "single-ended excitation" of the CMC, see Figure 9, with only one terminal being directly affected. To understand the behavior of the CMC in such an asymmetrical case of ESD disturbance, a TLP measurement method is applied as depicted in Figure 9.

Figure 9: Single-ended Excitation of CMC by TLP: quasi-common mode with high impedance, Terminal B "OPEN."

Here rectangular pulses of different amplitudes and a constant pulse duration of 100 ns are injected into one of the two CMC terminals, while the remaining one will be kept in floating condition. A constant TLP rise time is set to be in the range between 600 ps and 1 ns which is very similar to the IEC61000-4-2 standard (see Figure 5) to ensure comparability.

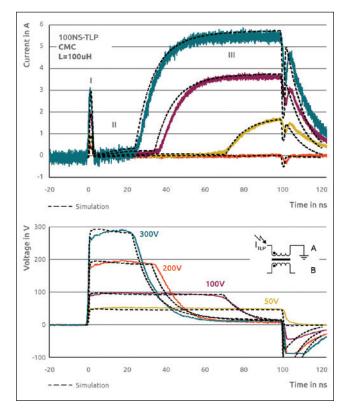

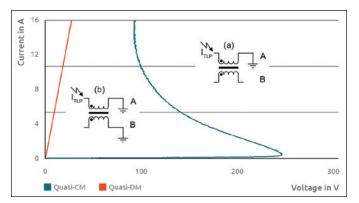

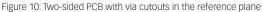

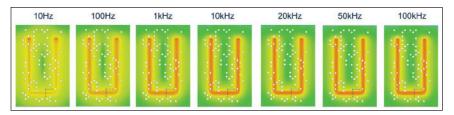

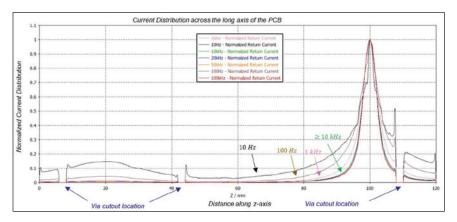

Figure 10 on page 20 shows the resulting complex transient TLP current/voltage response of the CMC with L=100  $\mu H$  in comparison to the corresponding simulation obtained with a CMC behavioral model (see dashed line), will be introduced later in this section.

Based on the transient curves, 3 characteristic regimes can be distinguished: dynamic (I) – voltage-dependent current overshoot in ns-range, a quasi-static regime of current blocking (II), and a current saturation (III). Those will be discussed in detail in the following.

#### Dynamic current overshoot (I)

It should be mentioned beforehand that a similar voltage dependent current overshoot in duration and amplitude as shown at the onset of the TLP current transient was observed in system-level ESD by the authors, see Figure 10, and reported in literature, see [7]. However, this 100 ns-TLP current peak is clearly related to a tester artefact caused by the distance of the CT1 current probe from the actual

# Coilcraft

# Cx Family Power Line Common Mode Chokes

- Solutions for use in a wide array of power line circuits

- Suppress high frequency common mode noise up to 100 MHz

- 1000/1500 Vrms isolation and up to 10 Amps Irms

- Low-profile, toroidal construction

# Free Samples @ coilcraft.com

DUT in the TLP setup, see HPPI application note [8]. In the first nanoseconds related to the propagation delay along the transmission line from the CT1 probe to the DUT and back, the 100 ns-TLP is blind to any current measurement except for the artefact peak.

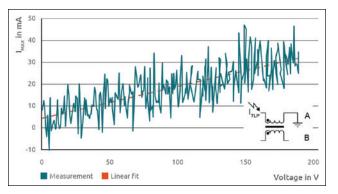

Since such an initial peak cannot be measured with standard 100 ns-TLP, vf-TLP was performed in the same single-ended excitation of terminal A with terminal B fully floating. Figure 11 shows the only small capacitive displacement current of up to 30 mA for a slew rate of about dV/dt ~ 200 V/ns at this operation point. Using I = C x dV/dt a coil capacitance of C = 150 fF can be estimated. This value is well in line with the 140 fF reported in [6] for high-impedance CM conditions only. Note that under DM operation the parasitic coupling coil capacitance increases significantly to C~10 pF. [6].

As mentioned above and discussed in Section III in our IEC system-level experiments, we can clearly observe an initial fast current peak of high amplitude similar to the 100 ns-TLP artefact. This peak is very relevant for IC system-level protection as well and far larger in the amplitude than the small current peak we would expect based on the results shown in Figure 11, where the standalone CMC operates in quasi-CM. So why do we observe such an assumed contradiction in CMC behavior when used in a system circuitry showing a first current peak related to a large DM capacitance, but a current blocking behavior related to a quasi-CM state? This question will be addressed in Section III.

#### Current blocking regime (II)

In phase (II) the CMC reveals initially a highohmic current blocking condition similar to the CM case. The difference of the quasi-Common Mode regime for the single-ended excitation with one of the CMC terminals fully floating, i.e., terminal B in Figure 9, is that no current is induced into the coil connected to the floating terminal of the CMC. As a result, no magnetic flux can develop by the second coil and suppress the magnetic flux initiated by the first one. Therefore, the CMC coil of terminal A appears for the entering pulse in its single inductance of L=100  $\mu$ H, as also reported in [5].

#### Saturation regime (III)

The onset of the CMC saturation is dependent on the voltage level across the excited CMC coil. The higher the voltage level, the earlier the magnetic saturation of the ferrite core occurs. Saturation leads to a significant increase of the current through the CMC, see Figure 10. In that case the current blocking capability

Figure 10: CMC with L=100  $\mu$ H: Transient 100 ns-TLP current / voltage response for Trise = 600 ps indicating 3 operation regimes I-III. Simulation (dashed lines) is compared to measurements.

Figure 11: vf-TLP peak current measurement in single-ended excitation of line A, line B fully floating (Quasi-CM): only small Imax. The straight line shows a linear fit through the datapoints.

of the CMC will be lost due to transition into lowimpedance or ohmic state. This detrimental behavior of the CMC for ESD should be carefully considered during the design of the Ethernet system and the ESD protection circuitry. Here, transient SEED simulation with an appropriate CMC model is a powerful tool for first-time right design. In the following, a behavioral CMC model will be introduced. Based on the observations, the Quasi-CM behavior of the CMC will be used for model tuning.

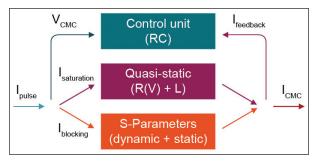

#### Behavioral model of CMC

In order to replicate the observed transient behavior of the CMC as shown in Figure 10 a dedicated behavioral model is implemented. Here, a modular approach is used to describe all 3 working regimes (I)-(III) of the CMC, see Figure 12. This blockdiagram represents how the model is implemented for one of the CMC terminals. For incorporation of both CMC channels the extended circuitry can be just mirrored along the S-Parameters block.

The core of the simulation is represented by S-parameters block, which includes all parasitics of the device and describes the interaction between

Figure 12: Equivalent circuit block-diagram for behavioral model of CMC (for one terminal) including (I) dynamic, (II) current blocking (static) and (III) saturation (quasi-static) working regimes.

# WE HELP YOU ALL THE WAY TO THE FINISH

Design Consulting – Compliance Assistance Product Testing & Certification Lab

#### **US-CAN-EU-International**

- Field Labeling

- Certifications

- Preliminary Reviews

- Design Assistance

- Environmental Testing

- Performance Testing

#### **Many Product Categories**

- Medical FDA Accredited!

- HazLoc Equipment

- ITE & Laboratory Equipment

- Appliances & Luminaires

- Alternative Energy

- Industrial Control Equipment

CertifiGroup.com • 800-422-1651 • 25,000 sq. ft. Lab • 100+ FREE Compliance Whitepapers

the CMC terminals. This allows us to emulate both the dynamic (current overshoot) and static (current blocking) regimes of the CMC. To fine tune the voltage overshoot an additional capacitance can be added in parallel to the blocking path. Modeling of the quasi-static behavior (II) covers the onset of saturation in dependence of the applied voltage level over time with the subsequent low-impedance state. For this purpose, the S-Parameters model needs to be extended with additional circuitry.

To realize the resistance change of the signal path, a voltage dependent resistor (switch) is connected in parallel to the signal path of the CMC. To provide smooth transition from high- to low-impedance state and describe current rise and voltage decay over time properly, an inductor is connected in series to the voltage dependent resistor as well. In addition, to fine tune the voltage offset in the low-impedance state a DC voltage source can be placed in series with the switch and inductor. Finally, to control the voltage change at the switch a control unit circuitry represented by an RC network and extended by a feedback loop are implemented. The latter is required to keep the reached control voltage levels for the switch during the whole saturation regime constant.

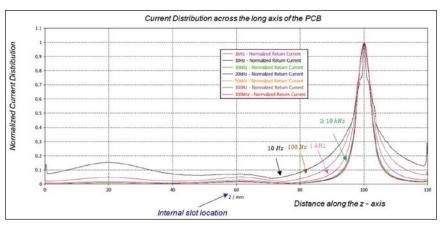

#### CMC key criteria for system ESD design

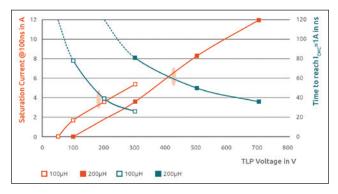

Besides the initial current spike (I) two criteria are relevant for the CMC's ESD blocking capability: a) the duration after which the CMC becomes low resistive, i.e., transparent for ESD due to transition from (II) to saturation (III), and b) the saturation current in the low-ohmic regime. Figure 13 compares these voltage dependent values for two different CMCs with L=100  $\mu$ H vs. 200  $\mu$ H in a 1210 and 1812 package respectively.

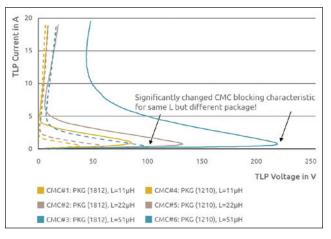

As expected, the lower inductance CMC transits faster from high-resistive current blocking mode into onset of saturation, thus losing the ability to "isolate" the IC from the ESD exposure faster. Moreover, the saturation current is significantly larger for the same TLP voltage as compared to the larger L=200  $\mu$ H due to a lower ohmic coil resistance. Furthermore, not only the nominal value of the inductance L of the chosen CMC impacts the ESD behavior as e.g., the onset point of saturation, but also the manufacturer specific package/dimensions and ferrite core geometry and material. Figure 14 gives an overview for CMCs in two different packages (of same manufacturer), but same inductance values characterized by TLP.

For same package configuration PKG (1812), we observe the same inductance dependence for saturation current and time to the onset of saturation as discussed above. However, it is important to note that different packages PKG (1812) vs PKG (1210) with same inductance exhibit entirely different ESD blocking capability. Consequently, to choose an appropriate CMC for system ESD protection we need to consider both inductance and package-type.

In the next chapter a system-level ESD analysis and risk assessment for multi-Gbit configuration will be performed taking into account the changed CMC

Figure 13: Comparison of two CMCs: L=100  $\mu H$  vs. 200  $\mu H$  regarding saturation current and time to the onset of saturation.

Figure 14: Comparison of CMCs in two different packages with: L=11  $\mu H$  vs. 22  $\mu H$  vs. 51  $\mu H$  regarding onset of saturation.

ESD blocking characteristic due to more challenging SI requirements of the high-speed data links.

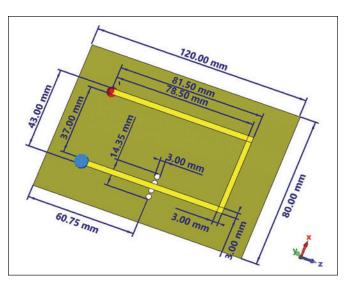

#### SYSTEM-LEVEL ESD ANALYSIS

For system-level measurements and SEED simulations Ethernet emulation network based on the specification [1] is used, see Figure 15. The decoupling capacitors of 100 nF are practically transparent for ESD pulses due to the very high dynamics of the ESD generator and, hence, do not impact the ESD behavior significantly. The CMT though seems to have an impact on the conduction state of the CMC as discussed below. The transceiver IC is emulated in a simplified but fairly critical way using a resistor network of 2-Ohm according to the OPEN Alliance specification [1].

#### **Ethernet ESD Behavior**

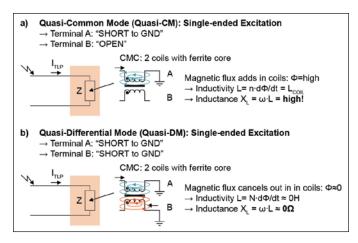

Figure 16 on page 24 shows a system level measurement and simulation for the residual current based on

Figure 15: Ethernet ESD current test circuitry including standardized IC emulation network formed by resistors [1].

100BASE-T1 network using a 4 kV ESD pulse according to IEC 61000-4-2. In general, the agreement between measurement and simulation is fair. The main characteristics can be captured by the simulation very well. Also, here the first peak can be clearly observed but compared to the TLP measurement in section II it is real and can be explained as follows.

www.raymondemc.com

# QUIET MATTERS.

# Whatever your project needs to shield, we can create it.

We design, engineer, build, and install quality turnkey, shielded enclosures and anechoic solutions to meet your project's requirements and specifications.

EMC Chambers | Deployable Chambers | Anechoic Chambers | Shielded Enclosures | Shielded Doors | Shielded Cabinets | Shielded Bags and Tents | Chamber Accessories | Consulting Services | Installations Services | Chamber Relocation Services | Maintenance/Repairs/Upgrades

#### sales@raymondemc.com

1-800-EMC-1495

The system-level ESD scenario in the Ethernet circuitry, as shown in Figure 15, differs from earlier discussed CMC analysis using TLP with floating coil B:

- Coil B is not fully floating but connected to the IC I/O with its internal ESD protection circuitry as emulated by the 2 Ohm resistor, same as coil at terminal A.

- A CMT network is connected to the CMC terminals at D+/D- thru the dc block (which can be neglected in the ESD time domain due to capacitance value)

In this configuration (see Figure 17) a modified CMC response is expected. Figure 18 illustrates the results for both singleended excitation cases, using TLP, where Terminal B is in one of two corner conditions: "OPEN" and "SHORT to GND".

The green curve represents the quasi-CM which was already introduced as a high-impedance state with transition into low impedance saturation. As opposed to this behavior, the red curve demonstrates the response of the CMC where terminal B is shorted to GND same as terminal A instead of floating.

Here we can observe that the CMC goes immediately into a low-impedance state with saturation regime, i.e., quasi-DM. Note that this configuration of terminal A and B on ground resembles the circuitry shown in Figure 15.

The result for quasi-DM condition contradicts the fact that we observe only a small residual current flowing into the IC, see Figure 16. That means, that CMC, being used in Ethernet circuitry acts in a high-impedance blocking state, as could be explained by quasi-CM, allowing the external ESD protection component to turn on and finally protect the IC.

Based on additional transient measurement on system-level, we developed a hypothesis to resolve this contradictory issue. Here, we considered the full board circuitry including the CMT network as a discriminating factor compared to our standalone CMC analysis. Figure 19 shows TLP time domain curves, where the CMT network including decaps is connected to the

Figure 17: Single-ended excitation of CMC by TLP: quasi-common mode with high impedance (a), quasi-differential mode with low impedance (b).

Figure 18: Single-ended excitation of CMC by 100 ns-TLP with  $T_r$ = 600 ps quasi-CM with second coil B fully floating, and quasi-DM with terminal A and B connected to ground, as illustrated in Figure 17 (a) and (b), respectively.

CMC from the left side and a 2 Ohm resistor terminates each of the CMC channels from the other side.

Here, no external ESD protection was connected between D+/D- and ground. Based on the results, we can conclude that a mix of two different operating modes occur for the CMC. At the onset of the pulse, during the first nanoseconds, the CMT is transparent and negligible for the entering TLP pulse. This is due to the fact the 1k-resistors are inflicted by parasitic inductance of several nH. Thus, the CMT circuit is an open which leads to a floating input of coil B. As shown in section III. A, this quasi-DM state has a low impedance and a high capacitance across the coil in the order of ~10 pF.

TLP measurement depicted in Figure 19 proves the differential operation mode due to the differential current peaks with same amplitude but different polarity. Those are likely a mixture of low-resistive DM response, plus as well as of capacitive coupling.

However, after some time the CMT network starts to shift the current phase between Terminals A and B of the CMC thus preventing the magnetic flux cancelation. As a result, the CMC transits into the high-impedance quasi-CM condition. Due to a relatively large time constant of the CMT  $\tau$  = R x C ~ 5 µs, the charging of the CMT capacitance should last during the entire ESD event keeping the CMC in the quasi-CM until saturation. In blocking mode, the CMC can strongly support the external ESD protection consequently avoiding any significant residual current into the IC during the entire ESD pulse, see Figure 19. In case the applied TLP voltage level is high enough, also the onset of saturation within quasi-CM regime can be observed.

For a system-level ESD protection it is obvious, that CMC alone is not capable to suppress the current initiated by the single-ended injection of ESD pulse and needs to be extended by an appropriate CMT network. In the full system circuitry, the CMC, CMT and the external ESD device are building a synergy significantly extending the entire system ESD robustness. On the one hand, the blocking characteristic of the CMC during the first nanoseconds helps to trigger the ESD protection

Figure 19: Single-ended excitation of D+ by 600 V 100 ns-TLP injection (system configuration see Figure 15 w/o ESD protection devices) where CMC shows a mix of two operating modes: Quasi-DM with current overshoot on both channels at first nanoseconds and Quasi-CM with current blocking and saturation regimes.

device. On the other hand, the ESD device takes the majority of the ESD current protecting consequently not only the IC, but rather the entire circuitry incl. CMC and CMT. A more detailed explanation based on a SEED simulation is given in the next subsection.

### ESD Risk Analysis of Multi-Gbit Systems by SEED Simulation

Next generation multi-gigabit data links such as automotive Ethernet or SERDES will definitely require different ESD protection devices and CMCs. However, no well-defined specifications for those components are available yet. Therefore, the authors make some plausible assumptions for electrical parameters of the ESD and CMC components to investigate the synergy effects of both components, see section III A, by transient SEED simulations.

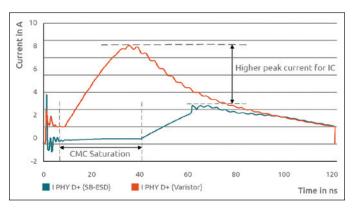

Firstly, a discrete ESD device with snapback and a larger holding voltage  $V_{hold}$  of 60 V is considered due to the trend to higher battery voltages for hybrids and electrical vehicles. Secondly, a CMC with reduced inductance L of 100  $\mu$ H is used due to higher data rates, hence, less inductance and parasitics will be added to the D+/D- in the context of signal integrity [1]. Figure 20 on page 26 depicts the results of the transient simulation for this example for 4 kV-IEC system-level stress.

As can be seen in Figure 20 (green curve), the nonlinear behavior of the CMC in conjunction with the ESD protection device turn-on behavior and clamping dynamics creates a critical current profile thru the sensitive IC I/O. Due to increased ESD clamping voltage (larger  $V_{hold}$ ) and the lowered CMC blocking capability (smaller L), the current into the IC I/O connected to the D+ data-line, would slightly exceed in its peak value at 60 to 70 ns a 4 kV-HBM IC robustness level.

In conclusion, this example of SEED simulation, extended with non-linear dynamic models of ESD protection devices at D+/D-, confirms the CMC working regimes from Section III.A when used within Ethernet circuitry: a) at the beginning CMC works in quasi-DM, as indicated in the simulation by two opposite current peaks at the onset of the pulse, followed by b) quasi-CM (current blocking mode), where the ESD current into the IC is almost blocked entirely. As a consequence, the voltage at the ESD protection starts to increase to the triggering level, at which it turns on and starts to shunt almost the entire IEC pulse to GND.

After a duration of approximately 40 ns, the CMC enters saturation, thus gradually losing its blocking capability. As a result, the current into the IC interface at D+ increases (green curve). Due to this competitive conduction with the CMC, the ESD device eventually starts to turn off at 60 ns, as soon as current and voltage levels at the ESD protection get too low to keep it further on. At this time, the CMC also reaches saturation (i.e., lowest impedance) while the current into the IC attains its maximum. This peak current slightly exceeds the 4 kV-HBM limit.

This simulation example clearly demonstrates the important synergetic protection mechanism of the ensemble of CMC and ESD within a complex system circuitry. Important to note in this context is that an enhanced ESD voltage clamping limits the residual IC current by two effects: a) the more trivial lower voltage exposure to the IC, b) the subtle effect of keeping the CMC for a longer duration in a current blocking mode before reaching low-impedance saturation.

The latter effect is highlighted by systemlevel simulation with a varistor in comparison to the snapback ESD protection in Figure 21. The higher clamping voltage of the varistor obviously provokes a much earlier onset of CMC saturation at

Figure 20: System-level 4 kV IEC simulation of Ethernet circuitry, see Figure 15, for a snapback ESD protection with  $V_{hold} = 60 V$  and a CMC with reduced inductance to L = 100  $\mu$ H. (a) Injected ESD pulse current, current through the ESD device at D+ and currents through both data lines (D+/D-). (b) Voltage at ESD protection at D+ node.

Figure 21: System-level 4 kV IEC simulation of Ethernet circuit, see Figure 15, with CMC L =  $100\mu$ H and different ESD protection: snapback ESD (same as in Figure 20) vs. varistor (Figure 2).

about 10 ns instead of 40 ns observed for the more effective snapback clamp. As a result, the current into the IC (PHY) reaches an almost three times higher peak value compared to the snapback protection as well as a significantly longer stress duration almost during the entire energetic part of the IEC pulse. Thus, the overall IC stress energy and risk of failure significantly increases.

#### CONCLUSION

This paper analyzes the future design challenges of system-level ESD protection for automotive highspeed data-links such as multi-gigabit Ethernet and SERDES. In particular, the impact of the changed ESD device requirements (increased holding voltage e.g., for higher board net voltage) and CMC limitations (lower inductance for better RF signal integrity) is investigated. Here, a special focus is put on an in-depth understanding of CMC operation during ESD event as standalone CMC and as device applied in the system. A clear CMC working regime classification is identified showing transitions from low-resistive quasi-DM to high-impedance quasi-CM to low-impedance saturation. In addition, the impact of inductance L and package variation for different CMC is investigated. As expected, the device reveals an increased ESD blocking capability with higher L for the same package type. However, also a different package appears to have a major impact on it even for the same manufacturer. Consequently, the inductance L is not the only figure of merit for choosing an appropriate CMC in view of protection against ESD during the initial system design phase.

For the SEED simulations on system-level described in the paper, the complex high-current CMC characteristic was incorporated into a non-linear behavioral CMC model. Applying both CMC and ESD non-linear dynamic behavioral models, the system simulation results clearly illustrate the synergy effects of CMC and the discrete ESD protection as also confirmed by appropriate measurements (TLP, IEC 61000-4-2). As major finding, it turned out that a lower ESD clamping voltage enabled by a welltuned, high-voltage snapback device offers a superior protection not only due to the trivial effect of less voltage exposure to the IC. Another strong second benefit is that the lower ESD voltage exposed to the CMC keeps the inductance for a longer duration in a blocking state. Thus, the IC is perfectly shielded

from the ESD until the CMC enters the lowresistive saturation mode. Such a prolonged blocking time can be sufficient to keep out the high-current, high-energy IEC peaks in conjunction with a welldesigned ESD component.

The paper highlights the benefit of a SEED simulation-based pre-design phase of the more advanced automotive high-speed links. Moreover, the tool allows an appropriate selection of external ESD and passive components to achieve a first-time right system ESD design in compliance with RF signal integrity.

#### ACKNOWLEDGMENTS

The authors would like to thank Shubhankar Marathe for valuable feedback during the paper review process.

#### REFERENCES

- OPEN Alliance, "IEEE 1000BASE-T1 EMC Test Specification for ESD Devices," Version 1.0, date 27.10.2017.

- 2. IEC 62132-4, "Integrated circuits Measurement of electromagnetic immunity - Part 1: General conditions and definitions," Edition 2.0, 2015.

- 3. IEC 61000-4-2, Edition. 2.0 Standard, ESD Immunity Test, 2008.

- Sergej Bub et al. "Efficient prediction of ESD discharge current according to OPEN Alliance 100BASE-T1 spec using SEED," ESD Forum, Germany, 2019.

- M. Ammer et al, "Characterization and Modeling Common Mode Inductors at High Current Levels for System ESD Simulations," EOS ESD Symposium, 2019.

- S. Mortazavi, "Characterization of Common-Mode Choke for Automotive Ethernet Networking enabling 100 Mbit/s," Proceeding of International Symposium on Electromagnetic Compatibility, September 2017.

- N. K. Kranthi et al. "Insights into the System-Level IEC ESD Failure in High Voltage DeNMOS-SCR for Automotive Applications," 2020 42nd Annual EOS/ESD Symposium (EOS/ESD), 2020, pp. 1–7.

- "How to Use Picoprobes and Flexible Pitch Probes," 2021. https://www.hppi.de/files/AN-010.pdf

# Join us in person at the 2023 EOS/ESD Symposium

The last three EOS/ESD Symposiums were offered in a hybrid format for presenters and attendees - facilitating virtual connection for those strongly impacted by pandemic-related travel restrictions. In 2022, more than 200 attendees and 36 exhibiting companies traveled to the Peppermill in Reno, NV, USA, and only 50 attendees participated virtually. The shift of attendees attending virtually in 2020 and 2021 to in-person in 2022 demonstrates the value and importance of face-to-face events and activities.

After considering many variables influencing a decision to host face-to-face-only events, the EOS/ESD Symposium will be on-site with no livestream connection in 2023. This decision means the Symposium strategy team can explore new ways to increase the interactivity that attendees truly value - the face-to-face and networking opportunities provided by an inperson event.

These opportunities include enhancing already established interactive sessions, such as workshops and hands-on demonstrations, and adding new initiatives. One focus is revamping the format of workshops with a task team already evaluating innovative solutions, such as interactive polling, a panel of invited speakers, and a new standalone session on the upcoming revision to the EOS/ESD Association, Inc. Technology Roadmap. We are introducing a new interactive session with members of the Association's standards working group activities and a new exciting electronic format for the

Author's Corner posters. Other exciting ideas include expanding the exhibit hall offerings with introductory tours to meet the exhibitors and demonstrations by exhibitors in their booths.

We appreciate your understanding and trust that EOS/ESD Association, Inc. has carefully considered the many impacts of hosting an in-person-only Symposium in 2023. With your support, EOS/ESD Symposium will continue to be the premier industry event. The 2023 Symposium Strategy and Steering Teams are excited about what's to come, and we hope you are as well!

We look forward to seeing you in person at the 2023 EOS/ESD Symposium at the Riverside Convention Center in Riverside, CA, USA

Electrostatic Discharge Association Setting the Global Standards for Static Control

#### **EXHIBITS OPEN**

**Monday** 6:00 PM - 9:00 PM

**Tuesday** 9:00 AM - 5:00 PM

Wednesday 8:30 AM - 2:00 PM

In Compliance thanks our advertisers for their support of our publication. Please visit their booths while at the show.

# ACL**Staticide**.

| BioFit Engineered Products402 |

|-------------------------------|

| Botron Company, Inc           |

| Conductive Containers, Inc    |

| Core Insight, Inc             |

| Cortec Corporation403         |

| Desco Industries, Inc         |

| Dou Yee Enterprises           |

| Electro-Tech Systems, Inc     |

| ESDEMC Technology LLC         |

# ESDEMC

| Estatec LLC                                     |

|-------------------------------------------------|

| ESTION Technologies GmbH404                     |

| Forbo Flooring Systems                          |

| GIBO/KODAMA Chairs113                           |

| Guangdong Btree New Energy Material<br>Co., Ltd |

| HANWA Electronic Ind. Co., Ltd 200              |

| Heebut Materials, LLC                           |

| HPPI Gmbh                                       |

In Compliance Magazine.104IONA Tech.401Kendall Howard.511Key Resin Company.405Mechnano.207NRD, LLC.502ORBIS Corporation.106Phasix ESD.206Siemens EDA.304Sika Corporation.107Simco-Ion Technology Group.409Spartech.105StaticStop, a division of SelecTech, Inc..107/112

# Static Stop

> StaticWorx GroundSafe® ESD Flooring

| Thermo Fisher Scientific        | 13 |

|---------------------------------|----|

| Top Talent Search Experts, LLC3 | 06 |

| Transforming Technologies4      | 13 |

#### StaticStop by SelecTech Booth 110/112

Come visit us at Booth 110/112 and see the most complete line of Static Control Flooring options available. We have resinous floor coatings, several glue-down options, interlocking options, carpet, rubber, all the maintenance products to keep your floor looking great and providing continuous static control. We are the market leader in Static Control Flooring and have been experts in the field for more than 20 years. Because we have such a complete line, we can help you choose the right product for your application. Visit us in Booth 110/112 or at https://staticstop.com.

#### StaticWorx Booth 114

An ESD flooring installation is only as good as its weakest component. Visit us at Booth 114 and learn why it's crucial to think of ESD flooring as a system, not a standalone product. Learn why it's critical to evaluate and specify flooring, furniture, chairs, casters and carts as an interdependent package that should be prequalified to ANSI acceptance standards. And why considering flooring as part of a system makes the most of your investment, ensuring the success of your ESD flooring installation. StaticWorx. We keep you grounded. Visit us in Booth 114 or call (617) 923–2000.

### https://esda.events

ith the focus on Quality over Quantity, the Symposium strategy team heard your schedule concerns and suggestions. In an effort to not dilute the quality of the event and address the lower attendance in Thursday sessions, we have restructured and streamlined the previous 3.5-day, three-parallel track event schedule. The 2023 EOS/ESD Symposium will be condensed to 3 full days - Monday morning, October 2, through Wednesday evening, October 4. Additionally, the parallel sessions will be reduced to two tracks for the entire duration of the event. We will continue to offer a selection of tutorials and the program manager certification exam before and/or after the Symposium. This redesigned schedule reduces the number of sessions required to fill the program, thus, allowing the team to focus on the quality of the event rather than the quantity.

| SATURDAY, September 30 |                                                                                       |  |

|------------------------|---------------------------------------------------------------------------------------|--|

| 8:00 AM - 5:00 PM      | FC340: ESD Program Development<br>and Assessment (ANSI/ESD S20.20<br>Seminar) - Day 1 |  |

| 8:00 AM - 5:00 PM      | ESD Compliance Verification<br>Technicion to TR53 - Day 1                             |  |

| 8:30 AM - 4:30 PM      | FC100: ESD Basics for the Program<br>Manager                                          |  |

| SUNDAY, October 1  |                                                                                             |

|--------------------|---------------------------------------------------------------------------------------------|

| 8:00 AM - 5:00 PM  | FC340: ESD Program Development<br>and Assessment (ANSI/ESD S20.20<br>Seminar) - Day 2       |

| 8:00 AM - 5:00 PM  | ESD Compliance Verification<br>Technicion to TR53 - Day 2                                   |

| 8:30 AM - 12:00 PM | DD/FC240: System Level ESD/EMI<br>(Principles, Design Troubleshooting,<br>& Demonstrations) |

| 8:30 AM - 4:30 PM  | FC101: How To's of In-Plant<br>ESD Auditing and Evaluation<br>Measurements                  |

| 1:00 PM - 4:30 PM  | DD134: Fundamentals of ESD<br>System Level                                                  |

| MONDAY, October 2   |                                                                  |  |

|---------------------|------------------------------------------------------------------|--|

| 8:00 AM             | Welcome                                                          |  |

| 8:00 AM - 8:35 AM   | Device Testing Invited Talk                                      |  |

| 8:00 AM - 5:00 PM   | ESD Compliance Verification<br>Technicion to TR53 - Day 3 (Exam) |  |

| 8:10 AM - 8:35 AM   | German ESD Forum E.V. Best Paper                                 |  |

| 8:35 AM - 9:25 AM   | Device Testing Papers 1A.1 & 1A.2                                |  |

| 8:35 AM - 9:25 AM   | GaN Invited Talk                                                 |  |

| 9:25 AM - 9:45 AM   | Author's Corner                                                  |  |