# THE COMPLIANCE INFORMATION RESOURCE FOR ELECTRICAL ENGINEERS

# Toward Standardization of Low Impedance Contact CDM

#### **PLUS**

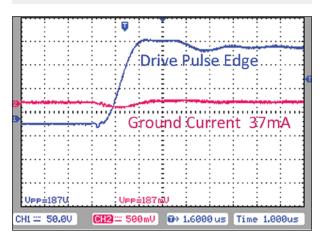

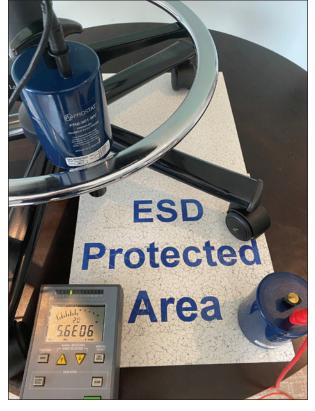

Static Control Flooring in High Reliability Environments

**System-Level Grounding**

Caster Contact: The Achilles Heel of ESD Floors

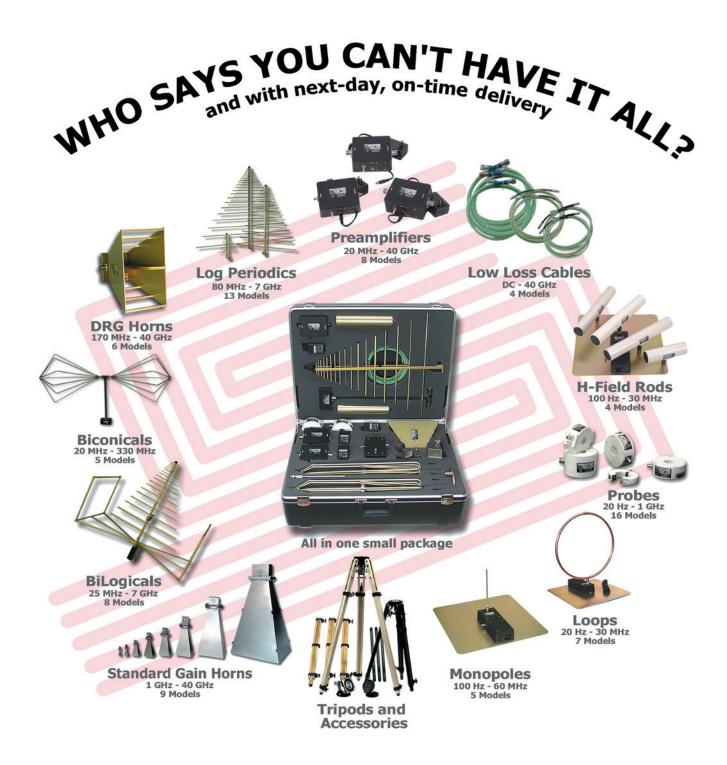

You Can Have It All when it comes to EMC/EMI testing. A.H. Systems is proud to bring you exciting new products, and many reliable favorites for your evaluation and compliance applications. Our antennas are unique and distinctive with broadband frequency ranges between 20 Hz up to 40 GHz. This enables us to specialize in various sales, rentals and, re-calibrations of test Antennas throughout the world. To view our products and get quick answers to your questions, access our comprehensive online catalog. Search for various information about product descriptions, typical AF plots, VSWR, power handling capabilities and links to product data sheets. Or simply request a catalog be sent to you. Not only have we been developing EMI Antennas for over 30 years, we also have organized worldwide sales representation. You can find your local knowledgeable representative in over 27 countries via our website. For quality products, excellent service

# 43rd EOS/ESD SYMPOSIUM AND EXHIBITS

September 26-30, 2021 The Westin La Paloma Resort and Spa, Tucson, AZ, USA

Full program and registration details: http://www.esda.org/symposium2021

# EXPLORE. INNOVATE. NETWORK.

This event features specially built modules with focused topics

Featuring a new hosting platform with state of the art attendee experiences

Discussions, workshops, author's corner, and demonstrations

While other conferences had "live" presentations that were simply pre-recorded videos, this year ALL presenters will either be live in person or live streaming their presentation. Nothing is pre-recorded!

Attend and be a part of how conferences should be run!

Education

Symposium

Co-sponsored by IEEE, EMC Society, The Electron Devices Society, and Reliability Society.

# <sup>™</sup>EERC™

electrical engineering resource center

Visit incompliancemag.com/EERC to access your free resources today!

THE CHALLENGES OF DELIVERING LARGE ANECHOIC CHAMBERS FOR TESTING LARGE EUTs

white paper provided by

**UNDERSTANDING**

DEBUGGING

ROHDE&SCHWARZ

HIPOT TESTING OF MILITARY/ AEROSPACE INTERCONNECT COMPONENTS

MAGNETIC FIELD CONVERSION

conversion guide provided by

**EMI PRECOMPLIANCE AND**

application note provided by

white paper provided by

**FACTORS**

#### ACCELERATED AGING WITH MIXED FLOWING GASES

**IOT REGULATORY COMPLIANCE**

white paper provided by

**NTS**

### lui Tangulalary Compliance Avenue

ebook provided by

In Compliance Magazine ISSN 1948-8254 (print) ISSN 1948-8262 (online) is published by

Same Page Publishing Inc. 451 King Street, #458 Littleton, MA 01460 tel: (978) 486-4684 fax: (978) 486-4691 © Copyright 2021 Same Page Publishing, Inc. all rights reserved

Contents may not be reproduced in any form without the prior consent of the publisher. While every attempt is made to provide accurate information, neither the publisher nor the authors accept any liability for errors or omissions.

| 14.1. (010) 100                     |                                                                                                                                                                                             |                                                                                                                              |  |  |  |  |  |  |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| editor/<br>publisher                | Lorie Nichols<br>Iorie.nichols@incompliancemag.com<br>(978) 873-7777                                                                                                                        |                                                                                                                              |  |  |  |  |  |  |

| business<br>development<br>director | Sharon Smith<br>sharon.smith@incomplianc<br>(978) 873-7722                                                                                                                                  | sharon.smith@incompliancemag.com                                                                                             |  |  |  |  |  |  |

| production<br>director              | Erin C. Feeney<br>erin.feeney@incompliance<br>(978) 873-7756                                                                                                                                | erin.feeney@incompliancemag.com                                                                                              |  |  |  |  |  |  |

| marketing<br>director               | Ashleigh O'Connor<br>ashleigh.oconnor@incomp<br>(978) 873-7788                                                                                                                              | ashleigh.oconnor@incompliancemag.com                                                                                         |  |  |  |  |  |  |

| circulation<br>director             | Alexis Evangelous<br>alexis.evangelous@incomp<br>(978) 486-4684                                                                                                                             | oliancemag.com                                                                                                               |  |  |  |  |  |  |

| features<br>editor                  | William von Achen<br>bill.vonachen@incompliand<br>(978) 486-4684                                                                                                                            | cemag.com                                                                                                                    |  |  |  |  |  |  |

| senior<br>contributors              | Bruce Archambeault<br>bruce@brucearch.com<br>Keith Armstrong<br>keith.armstrong@<br>cherryclough.com<br>Leonard Eisner<br>Leo@EisnerSafety.com<br>Daryl Gerke<br>dgerke@emiguru.com         | Ken Javor<br>ken.javor@emcompliance.com<br>Ken Ross<br>kenrossesq@gmail.com<br>Werner Schaefer<br>wernerschaefer@comcast.net |  |  |  |  |  |  |

| columns<br>contributors             | EMC Concepts Explained<br>Bogdan Adamczyk<br>adamczyb@gvsu.edu                                                                                                                              | Hot Topics in ESD<br>EOS/ESD Association, Inc<br>info@esda.org                                                               |  |  |  |  |  |  |

| advertising                         | For information about adve<br>Sharon Smith at sharon.sm                                                                                                                                     | rtising contact<br>nith@incompliancemag.com.                                                                                 |  |  |  |  |  |  |

| subscriptions                       | In Compliance Magazine subscriptions are<br>free to qualified subscribers in North America.<br>Subscriptions outside North America are \$129<br>for 12 issues. The digital edition is free. |                                                                                                                              |  |  |  |  |  |  |

Please contact our circulation department at circulation@incompliancemag.com

# SEPTEMBER 2021 CONTENTS

Volume 13 | Number 9

#### TOWARD STANDARDIZATION OF LOW IMPEDANCE 8 CONTACT CDM

#### By Nathan Jack, Brett Carn, and Josh Morris

The 16.6 ohm implementation of contact CDM (LICCDM) recently published in ANSI-ESD Standard Practice 5.3.3 is shown to produce waveforms of similar shape, I<sub>fail</sub>, and I<sub>neak</sub> vs. C<sub>eff</sub> dependency as JS-002. The non-monotonicity of JS-002 at low voltages is overcome using LICCDM. A path to joint standardization with air discharge testing is proposed.

#### Static Control Flooring in High Reliability Environments 22 By Tom Ricciardelli

High reliability organizations (HROs) typically implement stringent static control programs to mitigate the risks of catastrophic and/or life-threatening failures. This article describes some of the considerations to consider for static control flooring in these more demanding environments.

#### System-Level Grounding 28 By Vladimir Kraz

Grounding is often viewed from separate points of view - safety, ESD, or EMI. This article combines all these aspects together so that practitioners can address grounding at the factories and in the laboratories in a comprehensive way.

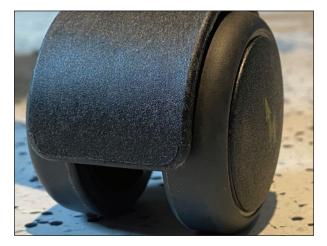

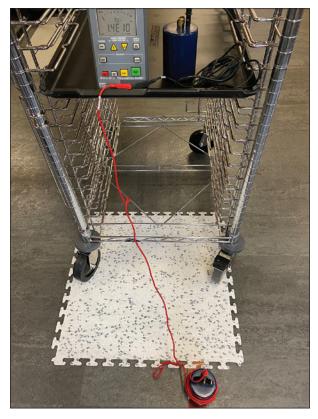

#### Caster Contact: The Achilles Heel of ESD Floors 42 By David Long

A fully functional ESD floor prevents static generation and provides an effective path to ground for personnel and equipment. Many conductive and dissipative floors meet STM 7.1 resistance parameters in ANSI/ESD S20.20 but fail to provide adequate electrical contact for grounding equipment with conductive casters and drag chains.

### 18 43<sup>rd</sup> Annual EOS/ESD Symposium

A Preview of the Symposium taking place in Tucson, Arizona September 26 - 30, 2021

6 Compliance News

- 40 Product Showcase

- 50 Advertiser Index

- 50 Upcoming Events

#### Boston, Raleigh to be Designated as FCC Innovation Zones

The U.S. Federal Communications Commission (FCC) has proposed adding Boston and Raleigh (NC) to its list of areas for advanced wireless communications and network innovation research.

According to a press release, Acting FCC Chairperson Jessica Rosenworcel proposed the additions to help expand the agency's efforts to help foster the development and integration of 5G network technologies and open radio access networks (RANs). If adopted by the Commission, Boston and Raleigh would join New York City and Salt Lake City under the agency's Innovations Zones initiative, which seeks

#### FCC to Require Electronic Filing of International Applications, Reports

The U.S. Federal Communications Commission (FCC) has extended its requirements for the electronic filing of applications and reports submitted to the agency for review.

The Commission will require that all reports and applications administered by its International Bureau be filed electronically through its International Bureau Filing System (IBFS). The expanded requirements will apply to Section 325(c) Applications, Applications for International High Frequency Broadcast (IHF) Stations, and Dominant Carrier Section 63.10(c) Quarterly Reports.

The FCC's Order also removes duplicate paper filing requirements for satellite cost-recovery International Telecommunications Union (ITU) declarations.

The Commission says that the decision to expand its mandatory electronic filing requirements is part of its overall efforts to streamline the filing process, reduce the costs for applicants, carriers, and Commission staff, and increase the transparency of this information. to expand the geographic areas where those holding experimental program licenses can conduct research and testing of these technologies.

The Boston Innovation Zone would be centered at Northeastern University, while the Raleigh Innovation Zone would be based on collaborations with North Carolina State University.

Rosenworcel's proposed changes to the Innovation Zones initiative would also expand the New York City Innovation Zone to include three Columbia University and City College of New York campus areas.

#### Report Addresses Fires Attributable to Lithium Batteries

As part of an effort to reduce the risk of fires caused by lithium batteries in waste electrical and electronic equipment (WEEE), a consortium of industry groups has just issued a report that compiles a number of "good practices" applicable to all phases of the product development process.

The report, "Recommendations for Tackling Fires Caused by Lithium Batteries in WEEE," compiles the findings of an industry survey conducted in 2019 by a consortium of EU-level associations of WEEE manufacturers and recyclers.

Part 2 of the report provides a compilation of the findings of that survey, listing nearly 30 different recommendations and good practices for reducing the risk of fires associated with WEEE batteries and addressing issues related to design, collection, and logistics, as well as policy matters.

The report makes clear that there is no "magic formula that will reduce to zero the risk of fires caused by WEEE containing batteries."

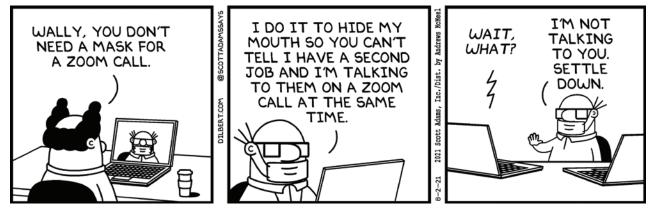

DILBERT © 2021 Scott Adams. Used By permission of ANDREWS MCMEEL SYNDICATION. All rights reserved.

#### EU Commission Updates Harmonized Standards for In Vitro Devices

The Commission of the European Union (EU) has updated its list of harmonized standards applicable to in vitro medical devices to reflect the latest available technical and scientific information.

According to Commission Implementing Decision (EU) 2021/1195, two new standards can now be used to demonstrate compliance with applicable requirements of the EU's In Vitro Diagnostic Device Regulation, (EU) 2017/745. These are:

- EN ISO 11737-2:2020, "Sterilization of health care products – Microbiological methods – Part 2: Tests of sterility performed in the definition, validation and maintenance of a sterilization process (ISO 11737-2:2019)"

- EN ISO 25424:2019, "Sterilization of health care products – Low temperature steam and formaldehyde – Requirements for development, validation and routine control of a sterilization process for medical devices (ISO 25424:2018)"

In addition, the Commission's Implementing Decision designated amendments to current harmonized standards, as follows:

- EN ISO 11135:2014/A1:2019, amendment to "Sterilization of health care products – Ethylene oxide – Requirements for the development, validation and routine control of a sterilization process for medical devices (ISO 11135:2014)"

- EN ISO 11137-1:2015/A2:2019, amendment to "Sterilization of healthcare products – Radiation – Part 1: Requirements for development, validation and routine control of a sterilization process for medical devices (ISO 11137-1: 2006, including Amd 1: 2013)"

Under Commission rules, compliance with an EU harmonized standard confers a presumption of conformity with the corresponding essential requirements in EU harmonization legislation once the standard has been published in the *Official Journal of the European Union*.

# TOWARD STANDARDIZATION OF LOW IMPEDANCE CONTACT CDM

Nathan Jack is engineering manager of the ESD/Latchup technology development team at Intel Corporation and can be reached at nathan.d.jack@intel.com.

Brett Carn is a principal engineer at Intel and can be reached at brett.w.carn@intel.com.

Josh Morris is an ESD engineering technician at Intel and can be reached at josh.p.morris@intel.com.

By Nathan Jack, Brett Carn, and Josh Morris

**Editor's Note:** The paper on which this article is based was originally presented at the 41<sup>st</sup> Annual EOS/ESD Symposium, where it was awarded the Symposium Outstanding Paper in 2020. It is reprinted here with the gracious permission of the EOS/ESD Association, Inc.

#### INTRODUCTION

The field-induced Charged Device Model (CDM) test method standardized in ANSI/ESDA/JEDEC JS-002 [1] is widely used for CDM qualification of integrated circuits. Because it relies on an air spark to initiate the stress, the pulse amplitude varies from zap to zap [2]. This discharge variation is increasingly significant as pre-charge voltage  $V_{pre}$  decreases [3].

Relay-based alternatives have been proposed to eliminate the variable air spark [2], [4]. Such "contact CDM" (CCDM) systems rely on transmission line pulsing and utilize 50  $\Omega$  coaxial cables and relays. It has been shown that 50  $\Omega$  systems generate pulses much wider than those of JS-002, but a better match can be obtained using lower system impedances. In [3], CCDM systems of 50  $\Omega$ , 25  $\Omega$ , and 11  $\Omega$ impedances were demonstrated. It was theorized that a 16.6  $\Omega$  CCDM system would provide the closest match to JS-002 in terms of waveform shape and the failure current (I<sub>fail</sub>) thresholds generated.

In this work, a 16.6  $\Omega$  "Low Impedance" Contact CDM system (LICCDM) is demonstrated. This system complies with the newly published CCDM Standard Practice 5.3.3 [5]. The waveform shape and I<sub>fail</sub> threshold generated during stress of a 32 nm test chip are compared against those of JS-002. It is shown that JS-002 produces non-monotonic peak currents (I<sub>peak</sub>) at low V<sub>pre</sub>. LICCDM is monotonic and enables low voltage testing with higher accuracy. LICCDM and JS-002 are shown to exhibit the same I<sub>peak</sub> dependency on the effective device capacitance C<sub>eff</sub>. Recommendations for merging JS-002 and LICCDM in a future standard are proposed.

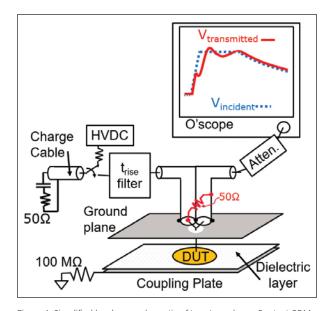

#### LICCDM

A simplified hardware schematic of LICCDM is shown in Figure 1. The charge cable is charged and then quickly discharged through a relay. A transmission line pulse is delivered through a rise time filter to the device under test (DUT) by way of a coaxial cable connected to the pogo pin. A second coaxial cable is connected in parallel to the first and delivers the transmitted pulse to an oscilloscope. A 50  $\Omega$  resistor is also connected between the pogo pin and ground. The effective impedance of the system as seen by the DUT is hence 50  $\Omega \parallel$  50  $\Omega \parallel$  50  $\Omega =$  16.6  $\Omega$ . Displacement current

Figure 1: Simplified hardware schematic of Low Impedance Contact CDM (LICCDM). Two coaxial cables – one for pulse delivery and the other for measurement – connect to the pogo pin along with a 50  $\Omega$  shunt resistor. The effective impedance of the system is thus 16.6  $\Omega$ .

stresses the DUT during the pulse rising edge. The RC termination results in a slow decay of the falling edge of the incident pulse, thereby preventing dual-polarity stress to the DUT. By subtracting the transmitted voltage waveform from the incident waveform and dividing by the system impedance, the current through the DUT can be determined [3]. The pogo pin is in contact with the DUT both before and after the stress; hence, the only spark that occurs is within the relay.

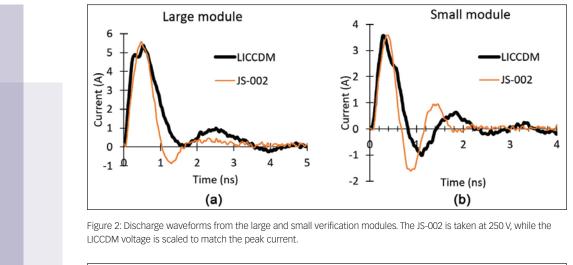

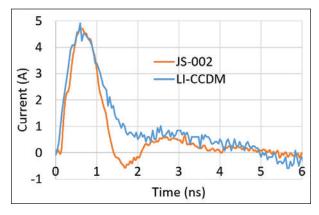

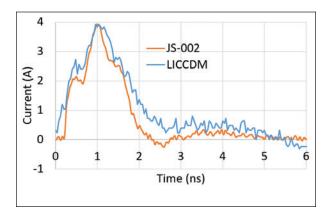

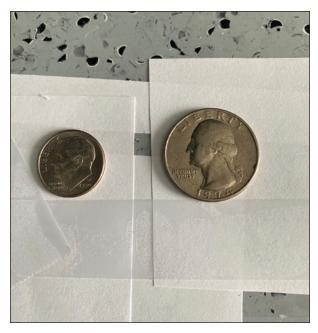

The LICCDM test head is used on a Thermo Fisher Orion2 tester. The waveforms generated when stressing the large and small verification modules (coins) on both JS-002 and LICCDM are shown in Figure 2. Because the effective RLC models of the two testers are similar, the waveforms generated share close resemblance [3]. The LICCDM V<sub>pre</sub> required to obtain a given I<sub>peak</sub> is approximately three times larger than that of JS-002. This is because the LICCDM  $V_{pre}$  is applied to the charge cable rather than directly to a field plate (JS-002). This charge cable  $V_{pre}$  is then divided as it travels through the transmission line network such that the actual voltage at the test head is approximately equal to the  $V_{pre}$ applied to the JS-002 field plate.

#### **TEST CHIP MEASUREMENTS**

LICCDM and JS-002 were used to stress a test chip fabricated in a 32 nm CMOS process. A 37mm x 37mm LGA package was used. Some pins of this chip were known to fail below 250 V, so characterization at low voltages was conducted to determine an appropriate step size and starting voltage.

#### Zap-to-zap variability

When characterizing a device to determine the CDM failure threshold, it is desirable to use a step

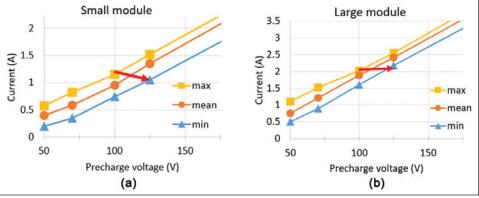

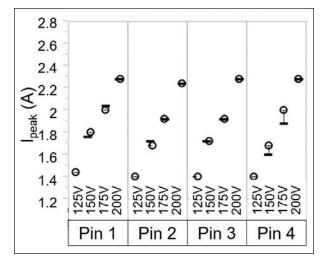

Figure 3: The max, min, and average  $I_{peak}$  measured during 50 zaps to the verification modules using JS-002. The red arrows indicate the non-monotonic behavior in  $I_{peak}$  that is possible when incrementing  $V_{pre}$  by 25 V.

When characterizing a device to determine the CDM failure threshold, it is desirable to use a step size that is a small percentage of the threshold being resolved.

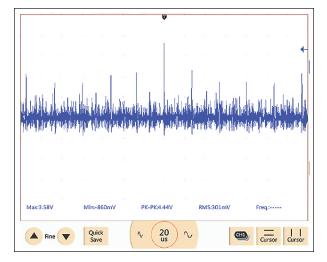

size that is a small percentage of the threshold being resolved. For example, while a 50 V step size in V<sub>pre</sub> may be adequate for resolving a failure occurring near 500 V, that same step size is relatively large when resolving a 125 V failure. However, it is well documented that air discharge CDM testing suffers from zap-to-zap variability arising from the variable nature of the spark [2], [3]. The step size must not be so small that the zap-to-zap variability in I<sub>peak</sub> is larger than the expected increment in I<sub>peak</sub>. Figure 3 shows the variation when stressing the small and large verification modules at various V<sub>pre</sub>. A 25 V step increase in V<sub>pre</sub> could result in no increase or even a decrease in I<sub>peak</sub>, as shown by the red arrow in Figure 3. Based on these data, testing with less than a 50 V step size would not be meaningful because I<sub>peak</sub> would be non-monotonic with V<sub>pre</sub>.

# ls your ESD floor caster compliant?

ESD floors ground more than people. Your floor must also keep carts, chairs and shelves at the same potential.

ESD chip floors, while they may pass a simple test like ANSI 57.1, solve only 50% of the problem. With a surface area the size of a dime, wheels and casters can slip into gaps between the chips.

StaticWorx ESD tiles provide 100% protection and are always caster-compliant.

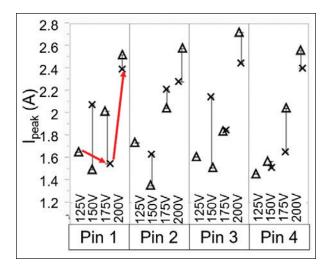

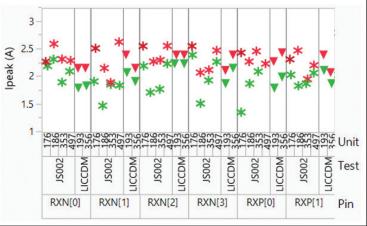

Figure 4: Measured I<sub>peak</sub> from stress to the test chip at a given V<sub>pre</sub> using JS-002. Data from single zaps to two units are displayed, both represented by a different symbol. A non-monotonic relationship with V<sub>pre</sub> is exhibited (red arrow).

The variation measured on verification modules is a best case scenario: the modules have a large, uniform surface on which to discharge. When testing a package pin,  $I_{peak}$  will also vary with pin shape and pogo pin alignment [6]. Figure 4 shows the  $I_{peak}$  obtained from two units when measuring four pins of the test chip using JS-002. A single stress to each pin was used at a given  $V_{pre}$ . In between each voltage step the unit was removed for parametric testing and then re-aligned before incrementing  $V_{pre}$ . The re-alignment procedure introduces another variable in the  $I_{peak}$  distribution. Despite 25 V increments to  $V_{pre}$  from 125 V to 175 V,  $I_{peak}$  actually decreases in some cases (red arrows in Figure 4). Increasing  $V_{pre}$  from 175 V to 200

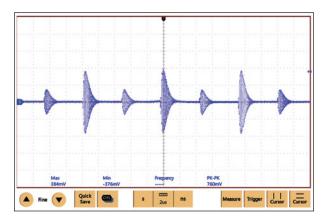

Figure 6: Test chip waveforms from a center package pin

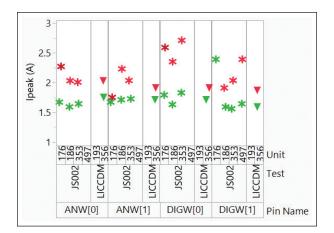

Figure 5: Measured  $I_{peak}$  from stress to the test chip at a given  $V_{pre}$  using LICCDM. Data from single zaps to two units are displayed, both represented by a different symbol.

V causes more than a 60%  $I_{peak}$  increase. These data indicate that even a 50 V step size is too small to avoid non-monotonic behavior; this makes it difficult to determine the true  $I_{fail}$  of the pin.

The same experiment is repeated using LICCDM to stress the test chip. Figure 5 shows a very repeatable, linear relationship between  $I_{peak}$  and  $V_{pre}$ . Because contact is made with the pin before the stress is applied, there is no air spark. Furthermore, minor differences in pogo pin alignment have no impact on  $I_{peak}$ . With zapto-zap variation eliminated, a very fine step size in  $V_{pre}$  can be used. This enables the true  $I_{fail}$  to be extracted, even at low discharge currents and voltages.

Figure 7: Test chip waveforms from a pin near the package edge

#### Pin location dependent variability

Sample waveforms from the test chip measurements are shown in Figures 6 and 7. Waveforms from the center of a package tend to be narrow, while those at the edge are wider and often have multiple peaks [7]. These variations are due to the parasitic elements of the discharge path *within* the DUT; charge from across the package takes longer to reach an edge pin than a center pin. LICCDM captures this natural source of variation which increases the likelihood of  $I_{fail}$  correlation with JS-002.

#### Failure threshold comparison

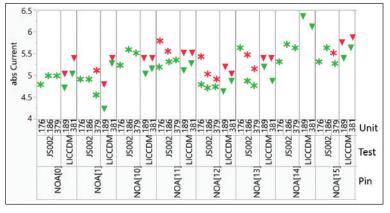

The  $I_{fail}$  of several different I/O circuits on the test chip were compared for both LICCDM and JS-002.

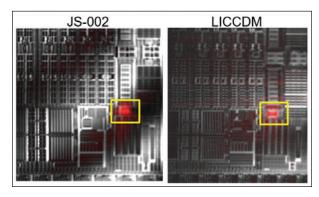

Figures 8 and 9 show the  $I_{fail}$  of various output driver pins. In all cases the output driver itself was the anticipated location of failure. The  $I_{fail}$ levels generated by both testers are comparable in Figure 8. In Figure 9 some unit to unit variation is observed for both JS-002 and LICCDM. This makes it more difficult to compare  $I_{fail}$ levels. However, the thermally induced voltage alteration (TIVA) analysis in Figure 10 on page 14 indicates that failures occurred in the driver transistors when stressed by both JS-002 and LICCDM.

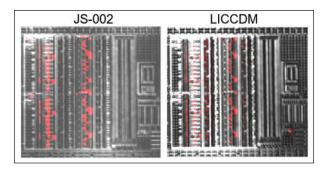

Figure 8:  $I_{\text{peak}}$  measured on four pins from multiple units. Green indicates no failure, while red indicates damage.

Figure 9:  $I_{peak}$  measured on eight pins from multiple units. Green indicates no failure, while red indicates damage. Unit to unit  $I_{rail}$  variation was more prevalent for this pin type, but the general trend aligns between both testers.

# Cx Family Power Line Common Mode Chokes

- Solutions for use in a wide array of power line circuits

- Suppress high frequency common mode noise up to 100 MHz

- 1000/1500 Vrms isolation and up to 10 Amps Irms

- Low-profile, toroidal construction

# Free Samples @ coilcraft.com

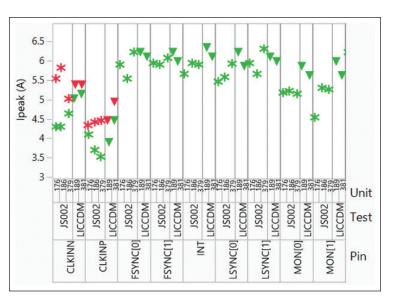

The test results from differential input pins with impedance matching termination resistors are shown in Figure 11 (all pins) and Figure 12 (CLKIN pins). The TIVA analysis in Figure 13 indicates failure in the termination resistor. Again, good correlation is observed between test types. The other pins in Figure 12 are general purpose input/output pins. No failures occurred on either test up to approximately 6 A.

#### $I_{peak}$ DEPENDENCE ON $V_{pre}$ , $C_{eff}$

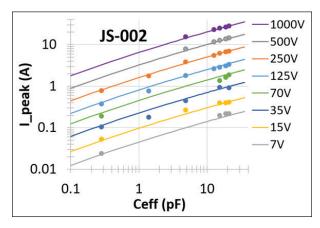

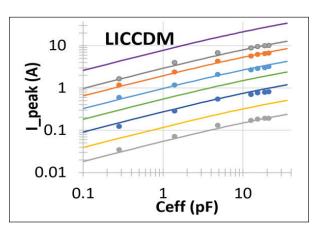

It was shown in [3] that CDM  $I_{peak}$  can be captured as a single, continuous function  $I_{peak} = f(V_{pre}, C_{eff})$ . In that work, the older "C101" air discharge test method [8] was used. This function is here applied to JS-002 (Figure 14) and LICCDM (Figure 15) using data taken on seven differently sized verification module coins. The area of these coins ranges from 4 mm<sup>2</sup> to 1500 mm<sup>2</sup>. A good fit across  $V_{pre}$ and  $C_{eff}$  is achieved. Note that the plots represent the maximum  $I_{peak}$  observed out of 50 zaps to each coin. While runt pulses are increasingly common and reduce the mean  $I_{peak}$  at low  $V_{pre}$  during air discharge testing [3], the maximum  $I_{peak}$  is very predictable down to single-digit  $V_{pre}$ .

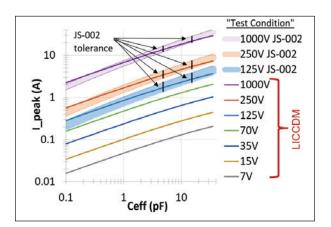

The models from Figures 14-15 are overlaid in Figure 16. The JS-002 standard has an I<sub>peak</sub> tolerance specified for two coin sizes at discrete "Test Conditions" (TCs) of 125 V and upward. These are indicated on the plot by solid black lines. The 1000 V, 250 V, and 125 V model curves from Figure 14 are thickened and shaded in Figure 16. The thickness represents the allowed JS-002 tolerance if it were extended across the entire  $C_{eff}$ range. While LICCDM (solid thin lines) is slightly less dependent on  $C_{eff}$  than JS-002, it can generate  $I_{peak}$  within the allowed JS-002 I<sub>neak</sub> tolerance using a set V<sub>pre</sub>.

#### **STANDARDIZATION**

While the LICCDM Standard Practice is a powerful CDM characterization tool, it cannot be used in lieu of JS-002 until it achieves Standard designation. This

Figure 10: TIVA image of a pin from Figure 9 showing the same damaged regions of the driver after JS-002 and LICCDM stress

Figure 11: I<sub>peak</sub> measured on six pins from multiple units. Green indicates no failure, while red indicates damage.

Figure 12:  $I_{\text{peak}}$  measured on nine pins from multiple units. Green indicates no failure, while red indicates damage.

section describes the importance of investigating LICCDM for inclusion in a future Standard and what the next steps and considerations should be.

#### The need for LICCDM in a standard

This paper has highlighted several undesirable characteristics of air discharge CDM testing: zap-tozap variation; sensitivity to pogo pin alignment; and non-monotonicity at low  $V_{pre}$ . These drawbacks will be increasingly impactful as design targets reduce below 250 V. Air discharge testing has other problems not addressed in this work. Packages with tight pin pitch are difficult to test with certainty because the spark from the pogo pin may strike any of the neighboring pins [9], [10]. Furthermore, the pogo pin may be larger than the pin being tested [9], [10]. Sharpening the tip can alter the onset of the spark generation and the corresponding waveform due to the corona effect [9].

Figure 13: TIVA image of an input pin from Figure 11 showing damage in the termination resistor after JS-002 and LICCDM stress

Figure 14: JS-002 I<sub>pask</sub> data (dots) from seven differently sized verification coins and the continuous function fit to the data (solid curves). The maximum I<sub>pask</sub> of 50 zaps is used to capture the worst scenario.

LICCDM overcomes all of the above-mentioned problems because the pogo pin contacts the device pin prior to discharge. In addition to eliminating zapto-zap variation, any uncertainty regarding which pin was stressed on a tight pin pitch package is also eliminated. A sharper, thinner pogo pin can also be used for testing small pins. This could conceivably be done at dimensions as small as the bare die level. The ability to test tight pitch, small dimension package pins will become increasingly important as package dimensions shrink to accommodate smaller form factors and faster signaling rates.

#### The need for more data

Given the decades-long history much of the industry has with air discharge CDM testing, it is highly desirable that any new test method replicate the stress and failure mechanisms of air discharge (i.e., JS-002

Figure 15: LICCDM I<sub>peak</sub> data (dots) from the same seven differently sized verification coins and the continuous function fit to the data (solid curves)

Figure 16: JS-002 model with  $I_{peak}$  tolerance (shaded thick, from Figure 14) compared to LICCDM model (solid thin, from Figure 15)

The industry must decide what degree of correlation is required between LICCDM and JS-002 before LICCDM can be adopted.

today). While this work and [3] have shown strong correlation between the two methods, a larger body of data is needed before LICCDM standardization.

An important first step is an industry-wide round robin to examine the  $I_{peak}$  vs.  $C_{eff}$  relationship of the two testers as was done in Figure 16. This can initially be done with verification module coins of varied sizes as was done in this work. JS-002 compliant testers from many manufacturers should be used along with multiple LICCDM tools.

Next, device level testing on a range of product applications and technologies should be conducted at multiple companies using both test methods. Failure mechanisms, locations, and I<sub>peak</sub> should be compared. While many CDM-induced device failures are driven by  $I_{peak}$ , others are driven by pulse rise time. Recent works have highlighted this as a potential source of miscorrelation when using relay-based alternative CDM test methods. In [11] it was postulated that a very fast-rising event occurs during air discharge testing as the capacitance between the pogo pin and the ground plane charges. This rapid event is not accurately measured by the disk resistor but was shown to be the likely cause of failure on a sensitive product. Relay-based methods were only able to replicate this failure by generating sub-100 ps rise times. The same was true in [12]; a miscorrelation between air discharge and relay-based Capacitively Coupled TLP (CC-TLP) was only resolved with sub-100 ps rise times. LICCDM and CC-TLP can generate these fast rise times, but it complicates the hardware setup. Given that the sub-100 ps rise time is not accurately measured on JS-002 today, relay-based testers like LICCDM and CC-TLP actually offer a more accurate alternative. A broader product study can help the industry decide how crucial it is to replicate these rapid rise time events and what the correct waveform would look like.

Finally, the industry must decide what degree of correlation is required between LICCDM and

JS-002 before LICCDM can be adopted. Given the drawbacks of JS-002 and the future direction of shrinking packaging technology and reduced CDM target levels, the benefits of LICCDM will likely outweigh infrequent miscorrelation.

#### Framework for a future CDM test standard

An inclusive CDM standard was proposed in [3] that would allow a wide range of test methods to be used interchangeably. Such an approach required a unique  $V_{\rm pre}$  adjustment for every DUT using a  $C_{\rm eff}$ -dependent look-up table. The results in Figure 16 suggest that a simpler approach can be taken: LICCDM can achieve the existing JS-002 tolerance specifications without a DUT-by-DUT  $V_{\rm pre}$  adjustment. If supported by round robin results, both air discharge and LICCDM (and possibly other methods) could be used interchangeably following nearly the same test procedure outlined in JS-002:

- Keep the existing JS-002 small / large verification module I<sub>peak</sub> + tolerance limits as-is. Add a third very small verification module (with corresponding limits) to be verified before testing very small devices.

- 2. Verify the tester by essentially following the JS-002 procedure. As is typical today with JS-002, the actual  $V_{pre}$  will not match the TC voltage. The software would apply a single scale factor to adjust  $V_{pre}$  such that the  $I_{peak}$  requirements are satisfied for all three modules. For LICCDM, this scale factor would be larger (approximately 3x) because  $V_{pre}$  is applied to the charge cable.

- 3. Specify the pertinent details of the waveform shape. It may be necessary to specify the rise time and pulse widths at multiple points (e.g., specify pulse width at 20%, 50%, and 80%). Product level correlation studies will inform these decisions.

- 4. Specify a TC above which either LICCDM or air discharge methods can be used. Below this TC, only LICCDM (or a similar relay-based tester

compliant to #1 - #3 above) should be used to avoid significant variability.

5. Report the results in terms of the legacy Test Condition voltage. The  $I_{peak} = f(V_{pre}, C_{eff})$  continuous function could optionally be published to inform users of the expected  $I_{peak}$  at any TC for a given  $C_{eff}$ .

#### CONCLUSIONS

LICCDM shows strong correlation with JS-002 across a wide range of  $V_{pre}$  and  $C_{eff}$ . The  $I_{fail}$  generated using either JS-002 or LICCDM were equivalent on a 32 nm test chip. LICCDM eliminates a number of problems inherent with JS-002 air discharge testing, namely: zap-to-zap variation, non-monotonicity at low  $V_{pre}$ , and inaccurate testing of products with tight pin pitch or small pin dimensions. A simplified approach to a standard inclusive of air discharge and LICCDM is proposed, allowing either tester to be used interchangeably. Further data collection is needed at multiple sites and on a variety of products to determine the limits to apply to waveform parameters (e.g. rise time).  $\mathbb{Q}$

#### ACKNOWLEDGEMENTS

The authors thank the ESDA/JEDEC CDM Joint Working Group for valuable discussion that shaped the direction of this work. The authors thank Thermo Fisher for manufacturing and loaning the LICCDM test head used in this work.

#### REFERENCES

- "Charged Device Model (CDM) Device Level", ANSI/ESDA/JEDEC, JS-002, 2018.

- R. Given, M. Hernandez, and T. Meuse, "CDM2 – A New CDM Test Method for Improved Test Repeatability and Reproducibility," *Proc. EOS/ESD Symp.*, 2010, pp. 359-367.

- N. Jack and T. Maloney, "Low Impedance Contact CDM," Proc. EOS/ESD Symp., 2015.

- H. Wolf, H. Gieser, W. Stadler, and W. Wilkening, "Capacitively coupled transmission line pulsing CC-TLP—A traceable and reproducible stress method in the CDM-domain," *Proc. EOS/ESD Symp.*, 2003.

- "Low Impedance Contact CDM as an Alternative CDM Characterization Method," ANSI/ESD, SP5.3.3-2018.

- 6. T. Brodbeck, K. Esmark, and W. Stadler, "CDM Tests on Interface Test Chips for the Verification of ESD Protection Concepts," *Proc. EOS/ESD Symp.*, 2007, 1A.1.

- J. Di Sarro, B. Reynolds, and R. Gauthier, "Influence of package parasitic elements on CDM stress," *Proc. EOS/ESD Symp.*, 2013, 9A.3.

- "Field-induced charge-device model test method for electrostatic discharge withstand thresholds of microelectronic component," JEDEC, JESD22-C101F, 2013.

- Industry Council on ESD Target Levels, May 2016, "White Paper 2: A case for lowering component level CDM ESD specifications and requirements."

- R. Ashton, M. Johnson, S. Ward, "CDM Testing of Small Integrated Circuits," *In Compliance Magazine*, June 2010.

- D. Johnsson, K. Domanski, and H. Gossner, "Device Failure from the Initial Current Step of a CDM Discharge," *Proc. EOS/ESD Symp.*, 2018.

- J. Weber et al., "Comparison of CDM and CC-TLP Robustness for an Ultra-High Speed Interface IC," *Proc. EOS/ESD Symp.*, 2018.

### Dear colleagues, friends, and ESD enthusiasts,

On behalf of EOS/ESD Association, Inc. and the 2021 Symposium Steering Committee, it is my honor to welcome you to the proceedings of the 43rd Annual EOS/ESD Symposium and Exhibits at The Westin La Paloma Resort & Spa in Tucson, Arizona. The EOS/ESD Symposium represents the world's leading forum on Electrostatic Discharge and Overstress. Although COVID-19 is still impacting our business and operations significantly, the Steering Committee and the Technical Program Committee, with all our great volunteers, spared no effort to ensure that the 43rd Symposium is a great experience for all attendees, on-site or virtually online.

In the 43rd EOS/ESD Symposium, the Steering Committee and the Symposium Strategy Team have structured the program in five focus areas, each with a program of 1-1.5 days. The focus areas are Advanced Technologies and Device Testing, Automotive, Communications, Mixed Voltage Applications, and, as in the last years, EMC. Each focus area comprises one or several sessions with technical papers, invited talks, tutorials, seminars, and workshops. For the first time, the Symposium started on Monday and was, therefore, one day longer than in the past, allowing more time for program and discussion. In parallel, for the fifth time, the "Manufacturing Track" offers full 3.5 days of technical sessions, hands-on sessions, workshops, discussion groups, and technology showcases in the field of EOS/ESD in manufacturing - control materials, technologies, and techniques.

The Technical Program Committee has selected 26 technical papers for the Symposium covering almost all aspects of the ESD world, including five technical papers for the Manufacturing Track. These papers were presented by experts from industry and academia, drive leading-edge research and development, and have been peer-reviewed by international experts. Additionally, the RCJ Best Paper authors have been invited to present their work at the EOS/ESD Symposium.

Wolfgang Stadler General Chair

In addition to the submitted technical papers, the Steering Committee invited world-leading experts to present their thoughts on the focus areas. Eleven invited talks and six seminars cover a broad spectrum of EOS/ESD-related topics. In addition, "Topic in Review" presentations address recent developments in the areas of analog and high-voltage technologies (Lorenzo Cerati, ST Microelectronics), CDM test methods (Nathan Jack, Intel), and high-speed communications (Kathleen Muhonen, Qorvo). Hands-on sessions and workshops in the Manufacturing Track focus on recent updates of the ESD control program standards ANSI/ESD S20.20, ESD TR53, and the new standard practice ANSI/ESD SP17.1 on ESD process assessment.

The EOS/ESD Symposium is the premier international event for professionals in industry and academia working in the field of EOS and ESD to meet and learn about the latest technical findings and innovative designs.

I hope that you will find useful information and new ideas in these proceedings!

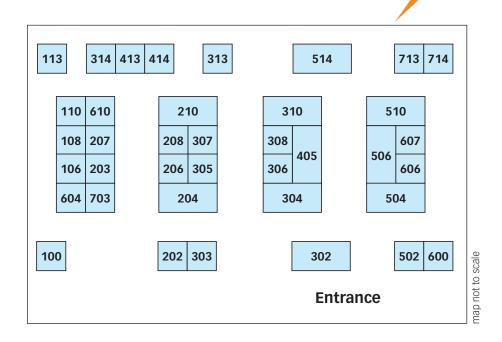

Sincerely, Wolfgang Stadler 2021 EOS/ESD Symposium General Chair Here are some of the tutorials, workshops, and sessions available during this year's event.

Visit https://www.esda.org/events/43rd-annual-eosesd-symposium-and-exhibits for the full schedule.

#### SUNDAY, SEPTEMBER 26, 2021

ESD Protection and I/O Design

System Level ESD/EMI (Principles, Design Troubleshooting, & Demonstrations

ESD Program Development and Assessment (ANSI/ESD S20.20 Seminar)

Design for EOS Reliability

Practical Applications of Ionization

#### MONDAY, SEPTEMBER 27, 2021

Mixed Voltage Applications

Advanced Design and Technologies

Manufacturing

ESD/EOS in Automotive Applications

5G Communication

#### **TUESDAY, SEPTEMBER 28**

Analog and High Voltage Technologies

**CDM Test Methods**

Manufacturing

#### WEDNESDAY, SEPTEMBER 29

ESD/EOS in Automotive Applications

EMC

Manufacturing

**High Speed Communication**

#### **THURSDAY, SEPTEMBER 30**

Automotive

EMC

Future Testing Methodologies

Manufacturing

# EOS/ESD Symposium Preview

#### **EXHIBITS OPEN**

| Monday    | .6:00 PM - 9:00 PM |

|-----------|--------------------|

| Tuesday   | 9:00 AM - 5:00 PM  |

| Wednesday | 9:00 AM - 1:15 PM  |

In Compliance thanks our advertisers for their support of our publication.

Please visit their booths while at the show.

| ACL Statici | de, Inc |  |  |  |  |  | 600 |

|-------------|---------|--|--|--|--|--|-----|

|-------------|---------|--|--|--|--|--|-----|

| <b>Barth Electronics</b> | , Inc |  |  |  |  |  |  |  |  | 313 |  |

|--------------------------|-------|--|--|--|--|--|--|--|--|-----|--|

|--------------------------|-------|--|--|--|--|--|--|--|--|-----|--|

| Ecolus                            |   |

|-----------------------------------|---|

| ESDEMC Technology, LLC 60         | 7 |

| Electro-Tech Systems, Inc 30      | 4 |

| Desco Industries, Inc 50          | 6 |

| DayStrong Rubber Products, LLC 30 | 5 |

| Dangelmayer Associates, LLC       | 4 |

| Conductive Containers, Inc 50     | 2 |

| Clean Control Tech Corp 51        | 4 |

| Botron Company, Inc               | 2 |

#### ESDEMC EXPERT ESD/EMC SOLUTIONS

| Estatec, LLC413          | 8/414 |

|--------------------------|-------|

| ESTION Technologies GmbH | . 300 |

| Forbo Flooring Sytems              |

|------------------------------------|

| GIBO/KODAMA Chairs                 |

| Grund Technical Solutions, Inc     |

| HANWA Electronic Ind. Co., Ltd 606 |

| HPPI GmbH 610                      |

| Magwel                             |

| NRD, LLC                           |

| ORBIS Corporation203Prostat Corporation204  |

|---------------------------------------------|

|                                             |

| Silicon Frontline Technology, Inc713/714    |

| Simco-Ion                                   |

| StaticStop, a division of SelecTech, Inc210 |

| Thermo Fisher Scientific       | 405 |

|--------------------------------|-----|

| Transforming Technologies, LLC | 510 |

### Industry Council Survey on Latch-up: A Brief Status Update

By Theo Smedes (NXP Semiconductors) for the Industry Council on ESD Target Levels

In July 2020, the Industry Council on ESD Target levels, in collaboration with the JEDEC JESD78 working group, launched a survey on Latch-up testing. An earlier article<sup>1</sup> in this magazine described the reasons for launching the survey and invited representatives from the industry to participate in order to collect data and opinions. The survey is now closed, but a full pdf version of the survey<sup>2</sup> is still available online. This article will give a short update on the results of the response analysis that is ongoing.

The Industry Council received 70 individual responses, from at least 35 companies from more than 16 countries. Multiple responses per company were encouraged because of the wide diversity of products, customers, and requirements. Although the survey was oriented at Revision E of the JESD78 standard, it is, of course, relevant to know which standards are actually used. The responses show that although other test standards and older JESD78 revisions are also used, the most prevalent standard in use is JESD78E. This gives good confidence in the relevance of the responses with respect to the survey's goals.

A high-level analysis of the responses shows interesting observations and allows preliminary conclusions:

- The responses give insight into the occurrence of Latch-up failures at different stages in the IC qualification process, application qualification process, and in the field. For example, answers to [Q06]3 show that the complaint rate for Latch-up based fails is low for most customers.

- A topic of debate in the Latch-up community is the definition of Latch-up. Historically, Latch-up is associated with the presence of a parasitic thyristor. From responses to [Q47], it can be concluded that the majority considers that the definition should be much broader. A significant group of respondents

agrees with the generic definition 'anything that causes sustained current increase'.

- Most respondents consider the Latch-up test method relevant, even with significance beyond the boundaries of the applied waveforms. Still, significant reservations to the usefulness are listed [Q09], and roughly 50% of the responses indicate that JESD78 alone is insufficient [Q49], [Q50].

- There is considerable disagreement on what should and should not be considered a Latch-up failure, but only 5% of the responses stated that the current (JESD78E) criteria were sufficient.

- The responses on questions related to Maximum Stress Voltage (MSV) and Absolute Maximum Rating (AMR), clearly suggest that in practice these are often equated. Since that is not the intent of the method, this feedback indicates that a better explanation is needed, possibly accompanied by additional education using webinars or tutorials.

All in all the survey results indicate that there is a need to improve the definition and understanding of the Latch-up test standard, as well as a need to cover broader ranges of applications. The full analysis of all responses is in progress and will be incorporated into a report that has recently been started. A more detailed analysis and summary will be presented at the 2021 EOS/ESD Symposium in September. This will be followed by the full report published by the Industry Council and JEDEC.

More information on the Industry Council on ESD Target Levels can be found here: http://www.esdindustrycouncil.org/ic/en.

Theo Smedes began work in ESD in 2000 and currently is Fellow for ESD, Latch-up, and EOS within NXP Semiconductors. He published several papers on ESD and introduced an ESD design course within NXP. Theo is a member of all ESDA device

testing working groups and is chair of the TLP working group. He has been a member of the Industry Council on ESD Target Levels since it was founded in 2006.

<sup>1. &</sup>quot;Industry Council Launches Survey on Latch-Up," In Compliance Magazine, July 2020, pp. 20-21

<sup>2.</sup> Full link to the survey: https://www.esdindustrycouncil.org/ic/docs/ latchupsurvey2020.pdf

<sup>3. [</sup>Qxy] indicates question xy in the survey document that can be found via the link mentioned in the text

# STATIC CONTROL FLOORING IN HIGH RELIABILITY ENVIRONMENTS

Special Considerations for Static Control Flooring for Added Risk Reduction

Tom Ricciardelli is the President and Founder of SelecTech, Inc., which makes a complete line of static control flooring systems sold through its StaticStop division. He has been involved in static control for more than 20 years and is an active member of the EOS/ESD Association, where he serves as Chairman of the Flooring and Healthcare committees. Ricciardelli can be reached at tricca@selectech.com.

By Tom Ricciardelli

S tatic control flooring is widely used throughout the electronics industry to provide a means to ground personnel and mobile equipment to control static charge generation and build-up. While I'd argue that it is always important to control static in an electronics manufacturing environment, there are some organizations where the risk of a device failure could have more serious consequences. This raises the bar in terms of managing the risk of failure and there are some things you should keep in mind when choosing static protective flooring to help with that.

#### WHAT IS HIGH RELIABILITY?

A group of researchers at the University of California, Berkeley, in their research to understand causes of major failures, identified certain organizations that were better at handling and avoiding these failures. <sup>1,2</sup> In their work, they defined a high reliability organization (HRO) as "an organization that has succeeded in avoiding catastrophes in an environment where normal accidents can be expected due to risk factors and complexity." They further defined the five principles that HROs have in common:

- Preoccupation with failure

- Reluctance to simplify

- Sensitivity to operations

- Commitment to resilience

- Deference to expertise

These principles have been adopted across many complex industries, including aerospace, defense, nuclear power, air traffic control, automotive controls, and healthcare, in which the major failures can have catastrophic and/or life-threatening consequences. Karl Weich and Kathleen Sutcliffe have studied several of these industries and how they adopt principles of high reliability. <sup>3,4,5,6</sup>

# HOW DOES THIS APPLY TO ELECTRONICS MANUFACTURING?

With the ubiquitous use of electronics to perform demanding and critical functions within the abovementioned industries, high reliability is an ongoing concern. Moreover, with the growing complexity of systems used throughout our environment, coupled with the increased complexity and miniaturization of devices, the concept of high reliability is becoming more and more commonplace in the electronics manufacturing industry, in general. In fact, the IPC standard for electronics assemblies, IPC-A-610, includes the following three classes for assemblies, with the most stringent being defined as High-Reliability Electronics Products: <sup>7</sup>

- Class 1 Electronics: General Electronics Products

- Class 2 Electronics: Dedicated Service Electronics

Products

- Class 3 Electronics: High-Reliability Electronics

Products

#### HOW DOES THIS APPLY TO STATIC CONTROL OF THE MANUFACTURING ENVIRONMENT?

In general, ANSI/ESDA S20.20 provides a framework for establishing a static control program for operations:

"...that manufacture, process, assemble, install, package, label, service, test, inspect, transport, or otherwise handle electrical or electronic parts, assemblies, and equipment susceptible to damage by electrostatic discharges greater than or equal to 100 volts HBM, 200 volts CDM, and 35 volts on isolated conductors."<sup>8</sup>

Within the ANSI/ESD S20.20 framework, flooring is primarily used as a means to ground personnel and mobile equipment. For personnel, it is intended to keep the voltage on personnel to below 100 volts and thereby ensure that any potential discharge from a person to a sensitive device falls below the limit of 100 volts HBM. To meet this objective, ANSI/ESD S20.20 set standards for flooring as follows:

- The complete system must have a resistance (pointto-point and point to ground) of less than 1.0 x 10<sup>9</sup> ohms as tested per ANSI/ESD STM7.1; <sup>9</sup>

- The complete system of person-flooring-footwear must have a resistance to ground of less than 1.0 x 10<sup>9</sup> ohms as tested per ANSI/ESD STM97.1; <sup>10</sup> and

- The complete system of person-flooring-footwear must generate less than 100 volts as tested per ANSI/ESD STM97.2.<sup>11</sup>

So, ANSI/ESD S20.20 is designed to control to 100 volts HBM. But what if the devices handled are more sensitive, that is, have a lower withstand threshold? For those situations, the standard simply states:

"Activities that handle items that are susceptible to lower withstand voltages may require additional control elements or adjusted limits."

Or, what if there is a desire to limit HBM to below 100 volts simply to increase the margin of error for preventing a failure? Or, what if there is a desire to increase the reliability of a static control program beyond what an ANSI/ESD S20.20 program would provide?

ANSI/ESD S20.20 is viewed as providing a minimum set of standards that meet a vast majority of the needs in factory-level ESD controls. End users, trained in ESD controls, can expand upon the ANSI/ESD S20.20 controls to create more stringent requirements for their particular applications and many HROs do just that.

#### HOW DOES THE ESDA VIEW HIGH RELIABILITY?

The issue of high reliability has become so prevalent within the ESD community that the Electrostatic Discharge Association (ESDA) has formed Working Group (WG) 19 – High Reliability to develop a guidance document to help users that may need or want to implement more stringent controls than those prescribed in ANSI/ESD S20.20. This work will include recommendations for nearly every aspect of ANSI/ESD S20.20.

Members of this working group are involved with some of the most stringent ESD control programs in the world and bring to this project their vast knowledge of ESD controls. While the work is not yet published, the working group meetings are open to guests. If you are interested in learning more about this work, go to http://www.esda.org/events for a schedule of upcoming working group meetings.

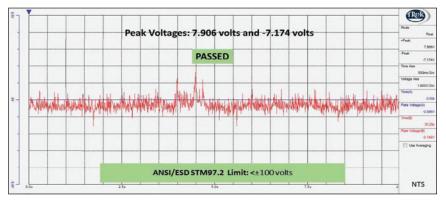

Figure 1: Walking voltage generated on a conductive floor

Figure 2: Walking voltage generated on a dissipative floor

#### CONDUCTIVE VS DISSIPATIVE FLOORING – MOST HROS CHOOSE CONDUCTIVE

With regard to static control flooring, the industry has historically used two "grades" of flooring, conductive and dissipative. These terms are defined in ANSI/ ESD STM7.1 as:

- Conductive flooring system has a resistance to ground of less than 1.0 x 10<sup>6</sup> ohms

- Dissipative flooring system has a resistance to ground of greater than or equal to  $1.0 \ge 10^6$  ohms to less than  $1.0 \ge 10^9$  ohms

But the electronics industry is moving away from classifying flooring by grade. As noted above, ANSI/ESD S20.20 simply requires that flooring have a resistance of  $<1.0 \times 10^9$  ohms, so either of these "grades" will meet the requirement as long as they also meet the requirement for the walking voltage test when tested in combination with the footwear to be worn in the area.

While the flooring/footwear combination is extremely important in determining the body voltage generation, all else being equal, the lower the resistance of the flooring, the lower the body voltage.

Figures 1 and 2 show the test results of body voltage generated for two flooring systems. In these tests, the flooring systems were nearly identical, with the first being formulated to have a resistance in the conductive range and the second having a resistance in the dissipative range. The footwear and the person conducting the test were the same in both cases.

As you can see, while both systems passed the requirement of ANSI/ESD S20.20, the conductive floor generated significantly lower body voltage, which

ing to customer wishes and easy extension from 16kV to 30kV using the same generator. Automatic network recognition means ESD3000 is always ready.

- up to 30kV air- and contact discharges

- Up to 3 test tips included

- > Charger & firmware update available

- > Rechargable long-life batteries

www.hvtechnologies.com

Mail emcsales@hvtechnologies.com Phone 703-365-2330

#### www.emc-partner.com

could be important in a very sensitive environment and would certainly reduce the risk of a potential failure due to an ESD event.

Also, as a floor gets dirty or ages, resistance levels may increase, potentially rendering the flooring-footwear system ineffective at achieving the desired level of protection. For these reasons, most of our HRO customers choose flooring that has a resistance of less than  $1.0 \times 10^6$  ohms. This provides an added measure of security that the floor will still perform when dirty and that body voltages will be kept as low as possible in the area.

#### FOOTWEAR

As previously noted, the ultimate test of protection and the resulting risk reduction is the amount of voltage that a person generates when walking on the floor and that this is affected by the combination of both the footwear and the flooring. There are a number of types of footwear available in the market, including:

- · Heel grounders

- Sole grounders

- · Conductive shoes

- Conductive booties

As mentioned, you must test the footwear that you intend to use with the floor you intend to use to ensure that you get the body voltage results that you require. The combination matters. I've personally seen a situation with a floor that tested consistently with a resistance in the  $1.0 \times 10^5$  ohms range, but the walking voltage test performed with the shoes actually used in that facility resulted in body voltage spikes greater than 100 volts. Fortunately, this was discovered in the planning stages and different flooring was chosen that worked extremely well with the footwear used.

One other thing to consider with regard to footwear is the contact that it has with the floor. Heel grounds offer the least, while conductive shoes and conductive booties have the most. The better the contact with the floor, the less likely someone will become electrically disconnected from the floor as they move across it.

#### UNDERSTAND THAT STATIC CONTROL FLOORING IS A SYSTEM

For any flooring system used in an ESD control program, it is important to understand the nature of the flooring system, the components it uses, and how they interact. So, for example, a conductive vinyl flooring system that is glued down includes the conductive vinyl tile, the glue, the substrate it is adhered to, and the grounding mechanism. Many of the epoxy/resinous coating systems used include a primer layer, a highly conductive ground layer, and a more decorative finish coat.

There have been many situations where one component in the system develops a resistance higher than desired, thereby causing the whole system to be out of compliance. In a high reliability environment, when choosing a flooring system, it would be prudent to understand all of these components and the risks associated with a potential failure in order to reduce the likelihood of a future non-compliance situation.

#### **REDUNDANCY WITH FLOORING**

In any quality system, adding redundancy reduces the probability of failure. In many high reliability applications, users will control static using wrist straps, ionization, equipment grounding, and packaging, to the point where flooring may not really be necessary. The floor provides a secondary means of grounding and protection in these environments and helps to ensure charges are kept to a minimum. Moreover, many HROs will increase the areas of coverage to include more ancillary areas to help ensure that any movements of devices are within an area with static protective flooring.

#### COMPLIANCE VERIFICATION OF FLOORING

ESD TR53 <sup>12</sup> provides compliance verification procedures for ongoing verification of control items used in an ANSI/ESD S20.20 control program. For flooring, some things to take into consideration for ongoing compliance verification include:

- The periodicity of testing: This is not prescribed in either ANSI/ESD S20.20 or TR53.The periodicity of testing should be regular enough to head off noncompliance, as determined by:

- *Use and maintenance:* If the floor is subjected to a lot of traffic and dirt, it may need to be checked

more regularly. Likewise, the regularity and extent of floor cleaning will impact how often the floor should be checked.

- *Life of electrical properties:* Some flooring systems have lifetime electrical properties, while others, such as applied finishes, only last a few months.

- *Any changes:* The floor should be checked if there are any changes in use or maintenance practices and materials. Any of these could impact the performance of the floor.

- *Past results:* By monitoring results over time, you can get a sense of if or how the floor is changing over time and adjustments can be made to periodicity as appropriate.

- Incorporating regular walking body voltage tests: The procedure in ESD TR53 for verifying flooring is a simple check of resistance to ground. As noted previously, the body voltage generation is a critical measurement of the effectiveness of a flooring-footwear system. As such, walking body voltage measurements should be taken periodically following the procedure of ANSI/ESD STM97.2. Doing so will help ensure that that flooring system and the flooring-footwear combination is still providing the desired static control.

#### CONCLUSION

While ANSI/ESD S20.20 provides a very strong framework for establishing an ESD control program, it does recognize that some organizations may need to enhance their program to meet their particular needs. HROs fall into this latter category and often will take added steps in their ESD control programs to reduce any potential risk of an ESD event leading to a failure. There are several things that an HRO can consider with regards to their static protective flooring system, including the resistance of the system, the footwear used in conjunction with that system, the extent of area covered, and the ongoing verification of the system.

#### **ENDNOTES**

Rochlin, Gene I., (1996-06-01), "Reliable Organizations: Present Research and Future Directions," *Journal of Contingencies and Crisis Management*, 4 (2): 55–59. doi:10.1111/ j.1468-5973.1996.tb00077.x. ISSN 1468-5973.

- Roberts, K.H., (1989), "New Challenges in Organizational Research: High Reliability Organizations," Organization & Environment, 3 (2): 111–125. doi:10.1177/108602668900300202.

- Weick, K. E., Sutcliffe, K. M., and Obstfeld, D., (1999), "Organizing for High Reliability: Processes of Collective Mindfulness," In B. M. Staw & L. L. Cummings (Eds.), *Research in* Organizational Behavior (Vol. 21, pp. 81-123). Greenwich, CT: JAI Press, Inc.

- 4. Weick, K. E., and Sutcliffe, K. M., (2001), Managing the Unexpected: Assuring High Performance in an Age of Complexity, First Edition, San Francisco: Jossey-Bass.

- Weick, K. E., and Sutcliffe, K. M., (2007), Managing the Unexpected: Resilient Performance in and Age of Uncertainty, Second Edition, San Francisco, CA: Jossey-Bass.

- Weick, Karl E., Kathleen M. Sutcliffe, 2001, *Managing the Unexpected – Assuring High Performance in an Age of Complexity*, San Francisco, CA, USA: Jossey-Bass. pp. 10–17. ISBN 978-0-7879-5627-1.

- IPC International, "IPC-A-610H: Acceptability of Electronics Assemblies," 3000 Lakeside Drive, 105N, Bannockburn, IL 60015.

- Electrostatic Discharge Association, "For the Development of an Electrostatic Discharge Control Program for Protection of Electrical and Electronic Parts, Assemblies and Equipment (Excluding Electrically Initiated Explosive Devices)," 7900 Turin Road, Bldg. 3, Rome, NY 13440.

- 9. ANSI/ESD STM7.1, EOS/ESD Association, Inc. "Flooring Systems Resistive Characterization."

- ANSI/ESD STM97.1, "Floor Materials and Footwear-Resistance Measurement in Combination with a Person STM97.1."

- ANSI/ESD STM97.2, EOS/ESD Association, Inc. "Floor Materials and Footwear – Voltage Measurement in Combination with a Person."

- ESD TR53, EOS/ESD Association, Inc., "Compliance Verification of ESD Protective Equipment and Materials."

# SYSTEM-LEVEL GROUNDING

Is Your System Well Grounded? Consider These Points in Effective Grounding

Founding is the most fundamental property of all types of electrical equipment. There are plenty of quality articles on specific subjects in *In Compliance Magazine* and in other publications, largely on grounding on a printed circuit board (PCB) level. This article focuses on a path less traveled, grounding on a system level, that is grounding of the equipment in actual use at the factories.

There are several key aspects of grounding, including safety, ESD, EMI, and signal integrity. While this and other magazines have published detailed articles on one or more of these subjects, this article combines them all to assist equipment users and tool makers in understanding what is important and how to achieve optimal ground performance. This article does not cover PCB grounding (there are plenty of excellent articles on this subject) and portable tools with double insulation that do not have grounding.

#### SAFETY

Safety is always first. Too many specialists in electrostatic discharge (ESD) and electromagnetic interference (EMI) are not professionally trained in electrical safety. This article is far from a comprehensive safety guide, and it doesn't cover every important safety point. The whole purpose of this section is to bring electrical safety Vladimir Kraz is the founder and President of OnFILTER, a California-based manufacturer of EMI filters, and also consults on EMI/ESD issues. He can be reached at vkraz@onfilter.com.

By Vladimir Kraz

to the attention of ESD and EMI specialists at factories and tool designers who otherwise may not be aware that grounding is a safety item. I strongly recommend that those who deal with such subjects take an electrical safety course, make friends with factory's licensed electricians, or join a factory safety committee. In this article, we will just scratch the surface and touch on the basics.

So why is grounding a safety element? As an example, let us consider a typical piece of industrial equipment, such as an integrated circuit (IC) handler, or surface mounted technology (SMT) pick-and-place machine (or any other tool that you are familiar with). Each of these tools takes its power from AC mains, meaning that typically anywhere from 100VAC to 440VAC enters the equipment. If a live wire inside such a machine or tool gets loose for whatever reason, it can touch and energize (that is, supply voltage to) a metal part to which an operator has access. Now this metal part, such as the enclosure, is under high voltage. The operator can easily be electrocuted simply by touching such a part.

Here is where grounding comes to the rescue. If all operator-accessible metal parts are properly grounded, an energized loose wire that touches such a part effectively short-circuits any live voltages to ground, and the resulting excessive current triggers the circuit breaker to cut power to the tool. For all this to work, these conditions must be met:

- All operator-accessible conductors must be grounded;<sup>1</sup> and

- The ground path must have a low enough impedance to allow a high current sufficient to trigger the circuit breaker.

How conductive should a ground path be in order to trigger the circuit breaker? There are several varying standards and guidelines on this subject, but the essential answer is that the ground path should be at least as conductive as either the live or neutral paths. If your power cable utilizes AWG12 (or 2mm diameter) power wires, you cannot have ground wires that are thinner than that. A ubiquitous AWG18 green wire just won't do.

Must all grounding wires inside the tool be as thick as the power wires that enter it? Not necessarily. In places where grounding is done for purposes other than safety (for example, ESD/EMI) and where there are no voltage-carrying conductors, grounding wires can be selected based on other criteria (see further on in this article).

#### **Ground and Neutral Reversal**

More often than desired, ground and neutral wires are reversed in either facility wiring or in the internal wiring of the equipment itself. This leads to return current flowing through ground rather than through the neutral wire, resulting in a multitude of functional problems in addition to being a safety issue. A ubiquitous three-LED outlet checker cannot detect that. The easiest way to check for it is to measure AC current on the ground wire entering the equipment using a simple AC current clamp (make sure to properly identify ground wire). If the equipment ground current exceeds 0.1 A during operation, an investigation is in order. This does not account for excessive leakage current in equipment even if the wiring is correct.

#### ESD

After safety, the second most common use of grounding in equipment is to address ESD considerations, more specifically, to provide a discharge path to ground for conductors and static-dissipative

Due to its construction, some equipment may have electrically floating metal parts, i.e., not electrically connected to anything. These parts are generally small. Special care must be exercised to assure that such floating pieces of metal physically cannot have electrical contact with live voltage.

materials. If accumulated static charges on electrically "floating" conductors and dissipative materials are not discharged to ground potential, they may carry unwanted voltage and cause problems for ESDsensitive devices.

How do we effectively ground such objects? Standards such as ANSI/ESD S6.1[1] and an "omnibus" standard ANSI/ESD S20.20 [2] provide good recommendations. Here we will add some helpful narrative.

It is curious to me that engineers and technicians dealing with grounding issues don't ask the most important and logical question about ground, that is, what is the voltage on ground? Not the resistance since resistance is just the means of reducing the voltage on grounded parts. The whole purpose of grounding for ESD purposes is to create an equipotential environment.

There are currently no coherent standards, standard practices, or technical reports issued by either the ESD Association or the IEC that touch this subject with any specifics on validation. Yet, this is the most important question for the safety of the devices in the process. The only document addressing it is SEMI Standard SEMI E.176 [3] which I'll cover later in this article.

How do we assure that what needs to be grounded actually is? There are implicit and explicit ways of providing grounding connections. Implicit ways include mechanical fastening of conductive parts of the tool to the grounded frame so that there are no obvious grounding wires, but the electrical connection via mechanical fastening is still present and is adequate. The problem with such implicit connections is that they are uncontrolled. Depending on the construction of the tool, any component in the electrical connection chain can be altered in the next revision of the tool or during repair or service and modified to the degree where the electrical connection is no longer assured. During any revision, maintenance, or repair, a metal washer can be replaced by a nylon one, or an originally bare metal part may become anodized, and so on.

There are two ways to prevent such problems. One way is to add requirements for adequate ground connection to the tool's specification and to the maintenance

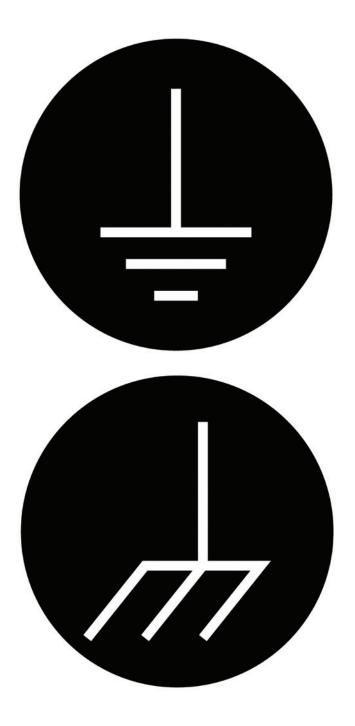

Figure 1: "Explicit" grounding in the IC handler

Figure 2: Grounding of moving parts using flexible steel cable

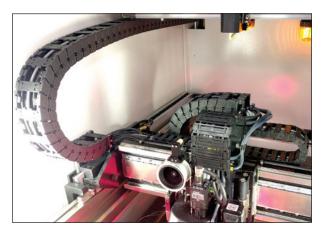

Figure 3: Flex cables on a robotic arm

procedure and verification documentation (and to meticulously follow it). Another way is to use an explicit, separate grounding method. Either of these methods is viable, and the choice is up to the user of the equipment since its manufacturer may not appreciate the importance of proper grounding for ESD.

An example of explicit grounding is shown in Figure 1. I'll come back to this figure later in this article.

#### ESD GROUND: HOW GOOD IS "GOOD"?

Various ESD-related standards such as ANSI 6.1, ANSI/ESD S20.20, ESD S10.1 [4], IEC 61340 [5], and some other documents, plus proprietary factorywide documents, provide guidance on grounding. This section simply attempts to provide clarification on some of the details.

#### Metal Ground

For "explicit" grounding and for the grounding of floating metal parts, these documents specify (or recommend) a resistance path to ground of less than 1 Ohm. While this goal is reasonably easy to achieve with stationary equipment, it can be quite elusive and not feasible for some of the moving parts.

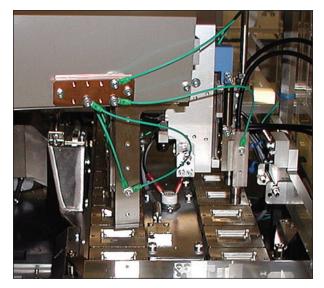

If the part moves just a little (even just a few centimeters, as is common in many tools) grounding is often done using flexible steel cable (quite similar to a bicycle brake cable, see Figure 2). Careful selection of material, flex radius, and the number of bend cycles of such cables is required to avoid breakage of the cable in use. Obviously, steel is not as good a conductor as copper, but it is much more durable. And, with very short cable runs, resistivity isn't really an issue.

Longer movements require much longer runs of ultraflexible cables protected by flex conduits, as shown in Figure 3. The internal construction of such flex cables does not support a sufficiently thick gauge of wire. Therefore, many ultra-flexible cables include an additional layer of Teflon or similar material around each wire that facilitates a low friction coefficient, allowing wires to slide against each other while bending.

This would be the case with any ultra-flex cables, with or without an external harness, as shown in Figure 2. The result is higher resistivity of such wires, making Quality & Service for EMC

Professional EMC Testing Solution Provider

# Electrostatic Discharge Simulators

#### EDS 20x(30x)Series

- > LCD touch screen

- > Built-in hygrothermograph for recording&protection

- > Automatic polarity switching

- > Max test voltage up to 30 kV

- > Replaceable RC modules, automatic detection of installed RC module

- > Long battery life for continuous tests

- > Enriched test standards library

- > Automatic detection of air discharge faults

- > Optional PC software control

As per:

IEC 61000-4-2, IEC/EN 61000-6-1, IEC/EN 61000-6-2, ISO 10605,

#### **EDS 10IC**

- > LCD touch screen

- > Automatic detection of installed RC module, automatic voltage adjustment

- > Accurate voltage setting, lower limit: 5 V, step: 1 V

- > Max test voltage up to 8 kV

- > Settable number of discharge, frequency etc, e.g. single time discharge

- > Manual or automatic discharging

As per:

Human Body Model (HBM), Machine Model(MM), ESDA/ANSI/ESD STM5.2:2009, ANSI/ESD-STM5.1: 2007, ANSI/JEDEC JS-001:2010, JEDEC JESD22-A114E:2007, JEDEC JESD22-A115C:2010, MIL-STD-883G:2006,-----

#### SUZHOU 3CTEST ELECTRONIC CO., LTD.

Add: No.99 Emeishan Rd, SND, Suzhou, Jiangsu, 215153, China Email: globalsales@3ctest.cn Ph: + 86 512 6807 7192 Web: www.3c-test.com

a 1 Ohm requirement of the entire connection almost unachievable, considering all the interconnects along the chain. Requirements to the total resistance of flex ground connections typically vary between 2 and 10 Ohms, depending on the factory, although I've seen 20 Ohms requirements as well. Would such an increase over 1 Ohm noticeably alter the ESD environment in the process? Actually, that's very unlikely, but what would cause the problem is a loss of ground connection.

The problem with the reliability of explicit grounding using dedicated conductors is that the failure of a ground connection may not be obvious right away. After all, such grounding or the absence of it does not alter the basic functionality of the tool and can go unnoticed for some time. I've witnessed an unfortunately large number of situations where "explicit" ground wires were disconnected for tool's maintenance but, instead of being reconnected, the wires were either completely removed or their ends were left "hanging," making the tool look a bit like a hedgehog. And these issues typically emerge when there's a need to resolve a "sudden" ESD or EMI problem.

One of the solutions to a lost ground problem is ground monitoring, and there are plenty of ground monitors on the market. Such monitors independently connect to the grounded point and to the reference ground and sound an alarm whenever a ground connection fails.

#### The 1 MOhm Question

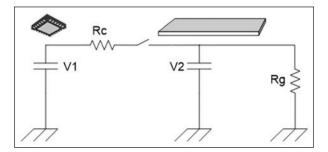

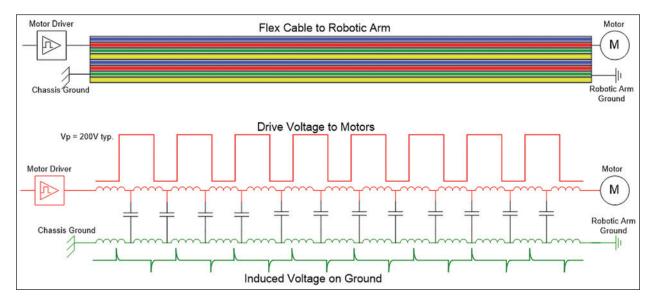

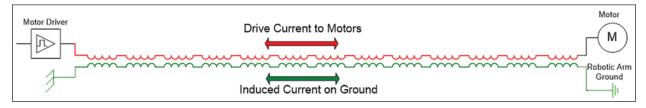

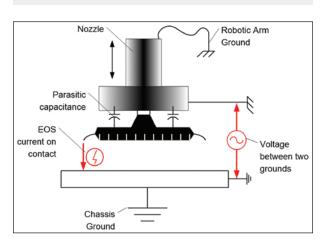

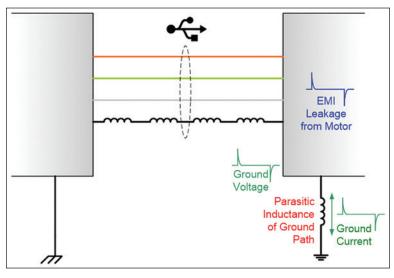

Wriststraps and/or wriststrap cords contain a 1 MOhm resistor in line with ground for a simple reason, that is, to prevent electrocution of personnel. Should an operator wearing a wriststrap accidentally touch a grounded conductor, the current through the operator should not exceed 0.5mA (ANSI/ESD S1.1 ANNEX B [7]), a limit that is consistent with several broader safety standards. At 250V RMS, which is the highest RMS AC voltage among common electrical outlets, the minimum resistance should be no less than 500 kOhms (not accounting for the electrical resistance of the operator's body). A 1M resistor would satisfy this requirement, including dual wriststraps that would have two resistors, electrically parallel to each other, between the operator's body and ground. Try to avoid low-cost wrist straps and cords unless their resistance is verified.