# THE COMPLIANCE INFORMATION RESOURCE FOR ELECTRICAL ENGINEERS

## Tackling Low-Voltage Signaling in Inverter Design

#### INCLUDING

Current Probe Specifications and Their Impact on Conducted Emissions Measurements

Laboratory Automation with PyVISA

ENGINEER'S TEST LAB HANDBOOK

## Does your antenna supplier do *all* this?

|                                      | Your<br>Supplier | A.H.<br>Systems |

|--------------------------------------|------------------|-----------------|

| Design / build their own?            |                  | ~               |

| 99% in stock now?                    |                  | ~               |

| Next day delivery?                   |                  | 1               |

| Over a hundred items to choose from? |                  | ~               |

| Portable antenna kits?               |                  | 1               |

| Still working after 10 years?        |                  | ~               |

| Over 80 years of experience?         |                  | 1               |

| Personal technical support?          |                  | ~               |

| Personal Customer Service?           |                  | 1               |

| Global support network?              |                  | ~               |

A.H. Systems does *all* of this, *all* of the time because we are the EMI test Antenna Specialists. We do not build "boxes". We do not build "Systems". We do design and build the highest quality, most accurate EMI test antennas (20 Hz - 40 GHz)

It may be more convenient to buy everything from one supplier, but remember "Your test system is only as good as the antenna you put in front of it!"

DRG Horns 170 MHz - 40 GHz 6 Models

All in one small package 20 Hz - 40 GHz

Biconicals 20 MHz - 18 GHz 7 Models

## **The Antenna Specialists**

## RETHINKING SOLID-STATE

### Think you know solid-state amplifiers?

#### THINK AGAIN!

Our latest solid-state amplifiers are redefining the limits of what this technology can achieve. With advanced combiner technology we're breaking new ground in power and frequency capabilities, traditionally dominated by TWT systems. Experience seamless scalability and high performance, including improved harmonic results, reduced warm-up time, and extended reliability with high MTTF.

Visit us at www.arworld.us Contact us at ari-sales@ametek.com or telephone 215.723.8181

Download the "Why Think Solid-State" infographic for a deep dive into the evolution of solid-state amplifiers!

##

The Premium Digital Edition

Whether you read In Compliance Magazine in print or online, we are committed to providing you with the best reading experience possible.

Our digital edition presents a responsive, interactive, and user-friendly version of the magazine on any device. Check us out online for exclusive bonuses.

HTTPS://DIGITAL.INCOMPLIANCEMAG.COM

In Compliance Magazine Same Page Publishing Inc. ISSN 1948-8254 (print) ISSN 1948-8262 (online) is published by

451 King Street, #458 Littleton, MA 01460 tel: (978) 486-4684 fax: (978) 486-4691

© Copyright 2024 Same Page Publishing, Inc. all rights reserved

Contents may not be reproduced in any form without the prior consent of the publisher. While every attempt is made to provide accurate information, neither the publisher nor the authors accept any liability for errors or omissions.

| publisher/<br>editor-in-chief       | Lorie Nichols<br>lorie.nichols@<br>incompliancemag.com<br>(978) 873-7777                                                                                                                          |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| business<br>development<br>director | Sharon Smith<br>sharon.smith@<br>incompliancemag.com<br>(978) 873-7722                                                                                                                            |

| production<br>director              | Erin C. Feeney<br>erin.feeney@<br>incompliancemag.com<br>(978) 873-7756                                                                                                                           |

| marketing<br>director               | Ashleigh O'Connor<br>ashleigh.oconnor@<br>incompliancemag.com<br>(978) 873-7788                                                                                                                   |

| circulation<br>director             | Alexis Evangelous<br>alexis.evangelous@<br>incompliancemag.com<br>(978) 486-4684                                                                                                                  |

| features editor                     | William von Achen<br>bill.vonachen@<br>incompliancemag.com<br>(978) 486-4684                                                                                                                      |

| senior<br>contributors              | Bogdan Adamczyk<br>Keith Armstrong<br>Ken Javor<br>Kenneth Ross<br>Christopher Semanson<br>Min Zhang                                                                                              |

| columns<br>contributors             | Bogdan Adamczyk<br>Erin Earley<br>Min Zhang<br>EOS/ESD Association, Inc.                                                                                                                          |

| advertising                         | For information about<br>advertising, contact<br>Sharon Smith at<br>sharon.smith@<br>incompliancemag.com                                                                                          |

| subscriptions                       | In Compliance Magazine<br>subscriptions are free to qualified<br>subscribers in North America.<br>Subscriptions outside North<br>America are \$149 for 12 issues.<br>The digital edition is free. |

|                                     | Please contact our                                                                                                                                                                                |

circulation department at circulation@ incompliancemag.com

## **DECEMBER 20** Volume 16 | Number 12

## FEATURE ARTICLES

Tackling Low-Voltage Signaling in 14 Inverter Design: Part 1

By Christopher James Semanson

24 Current Probe Specifications and Their Impact on Conducted Emissions Measurements

By Bruce Harlacher and Werner Schaefer

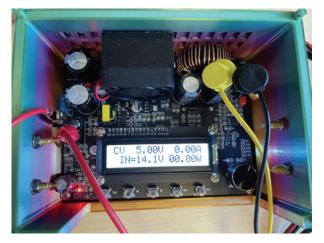

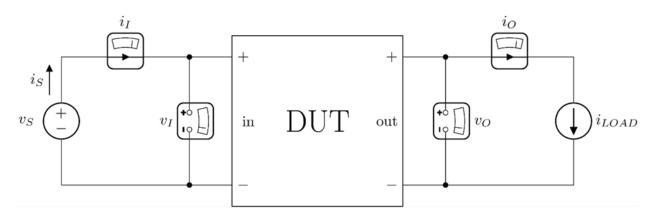

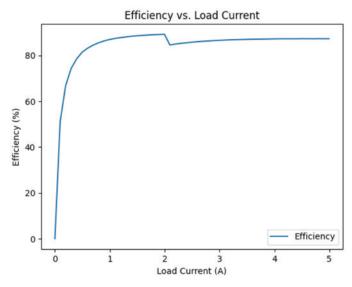

Laboratory Automation with PyVISA 34 By Dr. Zachary Nosker

## SPECIAL COVERAGE

#### The Engineer's Test Lab Handbook Δ1

**Obtaining NRTL Approvals** By Don MacArthur

Featured Resources Test Lab Quick Guide

## **COLUMNS**

- 52 EMC Concepts Explained By Bogdan Adamczyk

- 56 Hot Topics in ESD

- By James Davis, Greg O'Sullivan, Souvick Mitra, and Bong Andres for EOS/ESD Association, Inc.

## DEPARTMENTS

Compliance News Expert Insights 6 Upcoming Events Product Showcase 6 55 Letter to the Editor Advertiser Index

#### All Mobile Phones Must Be HAC, says FCC

The U.S. Federal Communications Commission (FCC) has adopted new rules requiring that all mobile phones available on the market be compatible with hearing aid technologies (i.e., hearing aid compatible, or HAC).

According to an FCC press release announcing the rule change, the new rules are the result of years of extended discussions and collaboration by members of the FCC's Hearing Aid Compatibility Task Force. Once

implemented, the 100 percent HAC requirement will provide an additional 48 million Americans dealing with hearing loss with the flexibility of choosing any model of mobile phone available to the general public.

In addition to the 100 percent HAC requirement, the FCC has also established a Bluetooth coupling requirement that will help to ensure connectivity between mobile handsets and hearing aids. Further, the FCC

rules also require that all newly introduced mobile handsets meet volume control requirements that allow users to adjust handset audio volume without introducing distortion.

Mobile handset manufacturers have 24 months to comply with the FCC's new HAC requirements. Nationwide service providers are given a transition period of 30 months, while non-nationwide service providers have 42 months.

#### FDA Classifies Radiofrequency Toothbrush as Medical Device

As new and emerging technologies continue to define and influence our lives in the 21st Century, regulators must work to ensure that their own efforts reflect the latest technology developments and address potential regulatory and safety concerns.

The case is perhaps most interestingly illustrated by a decision by the U.S. Food and Drug Administration (FDA) regarding its review of an electric toothbrush that uses radiofrequency (RF) waves to remove plaque and stains from teeth. Developed by the company Home Skinovations Limited, the ToothWave<sup>™</sup> electric toothbrush uses patented RF technology to direct RF waves to the teeth and gum line. The company claims that the RF waves destabilize impure molecules that bond to teeth and replaces them with new, purer molecules that provide a stronger protective layer.

The company submitted a De Novo classification request regarding the device to the FDA back in 2019. After a year-long extensive review, the FDA classified the toothbrush as a Class II device, that is, a device that requires specific "special controls" to provide reasonable assurances of the safety and effectiveness of the device for its intended use.

In the latest development, the FDA has now modified its regulations under 21 CFR Part 872, adding a "radiofrequency toothbrush" as a regulated device. In a Final Amendment and Final Order, the FDA now defines specific requirements applicable to this advanced dental care product that are intended to mitigate potential risks to health associated with the use of such a device.

#### **ARRL Releases Updated Amateur Radio Handbook**

The National Association for Amateur Radio (ARRL) has announced the release of an updated version of its classic guide to amateur radio technology and practice.

According to a press release posted on the ARRL website, the newlyreleased 101st edition of The ARRL Handbook captures "the state of radio science and technology in one

authoritative work." The six-volume set spans over 1200 pages and provides a "deep dive" into radio electronics, circuit design, digital modulation techniques, and equipment construction.

Important updates to the latest edition of the Handbook include:

Information on electromagnetic analysis, as well as cost-effective tools for modeling circuits, antennas, and propagation;

- Radio astronomy receiver and antenna design information;

- A newly added section on batteries and battery safety; and

- Updated information on RF safety and compliance with FCC exposure regulations.

#### Thank you to our Premium Digital Partners

### Upcoming Events

#### December 3-5, 2024 Fundamentals of Random Vibration

January 28-30, 2025 DesignCon 2025

and Shock Testing Training

#### LETTER TO THE EDITOR

The article in the November issue "Portable Electronics Onboard Aircraft" was quite informative. It is my understanding that the problem first arose when passengers' FM broadcast receivers interfered with communication and navigation signals. The FM broadcast band runs from 88 to 108 MHz, and the aircraft communication and navigation band runs from 118 to 137 MHz, with additional VOR navigation between 108 and 118 MHz.

Since the local oscillator in an FM superhet receiver normally runs 10.7 MHz (the IF) above the receiving frequency, and since the oscillator is rarely shielded against stray emissions, its radiation will almost certainly interfere with the aircraft's communication or navigation when a passenger's receiver is tuned between 97.3 and 108 MHz. Interference from other portable electronics arose in later years.

— Jonathan Allen

MILITARY AND AEROSPACE EMC

Portable Electronics Onboard Aircraft Part 1

#### FROM THE AUTHOR

Thank you for the kind words and thank you for the additional information. Superheterodyne receivers do have a known ability to transmit at their local oscillator frequency,

READA IN COMPLANCE | 11

which is how the police can detect the use of radar detectors (called a radar detector detector of course).

— Patrick André

## EMC BENCH NOTES Embedded Processor Characterization and Design Review

By Kenneth Wyatt

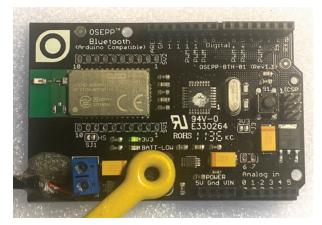

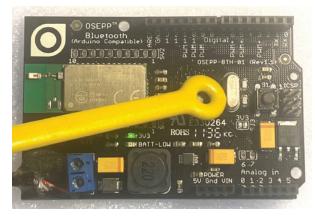

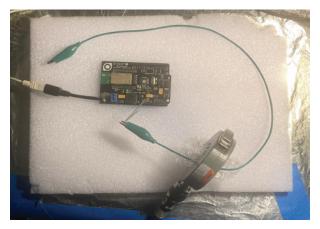

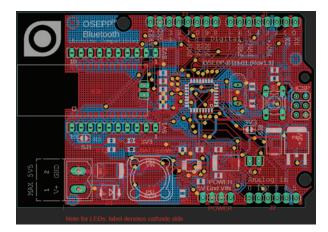

Let's use the basic tools and spectrum analyzer setup I described *in the last two months* and use them to characterize an actual embedded processor board based on the Arduino design. I'll be using an "OSEPP Bluetooth" board, but you can use anything on hand or similar (Figure 1). The schematic and board layout are available in Reference 1. While most Arduino-based boards use linear regulators, I chose this board from my collection because it includes a DC-DC converter and uses a two-layer design with obvious EMC issues.

Figure 1: Our example unit under test is an Arduino-based single-board embedded processor with Bluetooth.

Figure 2: Probing the DC-DC converter switching currents by coupling the medium-sized H-field loop to the switching inductor, L1.

#### CHARACTERIZATION

This is a great board to evaluate and characterize for EMC issues. It is a two-layer board with ground fill but no solid return planes. It also includes an onboard DC-DC boost converter with a three-terminal 3.3V linear regulator. The processor is an ATMEGA328P with an external 16 MHz crystal clock. There is no other circuitry on the board other than the Bluetooth module, which we won't be evaluating.

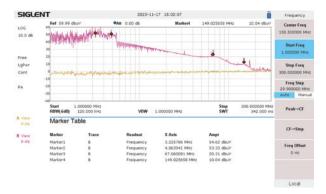

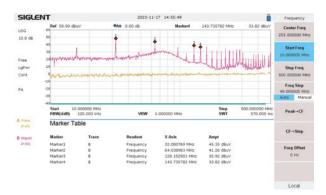

Let's make some near field probe measurements; first on the DC-DC converter. This is easy to identify because of the large  $22\mu$ H inductor at the bottom of the board. We'll non-invasively couple to the inductor (Reference 2), which is connected to the MAX1676 boost converter. Figure 3 shows the resulting frequency domain plot. Placing the spectrum analyzer in Max Hold mode, we can see a lot of switching energy extending out to 200 MHz. You'll notice that for each plot, I record the system noise floor (yellow trace). I also placed markers at some of the resonant peaks, which we may use in possible future analyses.

In addition, probing around the processor (Figure 4) reveals a lot of 16 MHz harmonic energy along with the broadband energy from the DC-DC converter (Figure 5).

Note that to confirm these narrow band harmonics are indeed 16 MHz, I have placed markers 3 and 4 on adjacent peaks. Subtracting the two frequencies confirms this.

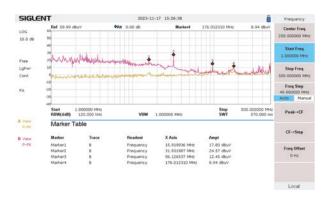

Now, let's clamp our current probe around the DC power input cable (Figure 6). I've inserted some "bubble wrap" around the power cable to help isolate it from the metal case of the probe. Here, we observe very strong broadband switching noise with a 16 MHz peak (Figure 7).

Figure 3: The resulting plot of the DC-DC converter. Note the broadband energy extends out to 200 MHz. The yellow trace is a record of the system noise floor.

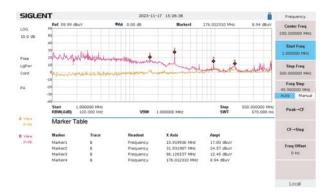

Now that we've characterized the high-frequency currents traveling along the power cord, how about measuring the harmonic energy of a wire connected to the system ground return? This would represent an I/O cable, such as a USB, attached to the board (Figure 8).

Using a standard paper clip pushed into the "Gnd" socket and connecting a short clip lead, I measured the

Figure 4: Using the medium-sized H-field probe to characterize the 16 MHz clock harmonics. These narrow band harmonics extend past 500 MHz.

Figure 5: It is easy to observe the 16 MHz clock harmonics that extend past 500 MHz. The yellow trace is a record of the system noise floor.

Figure 6: Using an RF current probe to measure the high-frequency harmonic currents flowing along the DC power cord.

emissions in Figure 9. Note that we still see the broadband emissions from the DC-DC converter, as well as several 16 MHz harmonics from the processor clock.

Figure 7: Not only is there the usual broadband EMI due to the DC-DC converter, but we also observe several 16 MHz clock harmonics. These would likely cause radiated emissions. The yellow trace is a record of the system noise floor.

Figure 8: We can simulate an I/O cable, such as USB, by connecting a wire to the system ground return and measuring the high-frequency harmonic currents using an RF current probe.

Figure 9: The harmonic currents measured on a short wire connected to the PC board ground return. There is a resonance at 128 MHz, the half-wavelength of the power cable, board, and wire combination. The yellow trace is a record of the system noise floor. Note the interesting broad peak at 128 MHz. This is a half-wave resonance due to the combined length of the power cord, circuit board length, and attached wire. These physical resonances can reduce the margin or even throw you over the limit if not mitigated.

#### **MITIGATION SOLUTIONS**

Let's find out why this board is so noisy! Looking at the top and bottom layers reveals the main issue, and that is no solid return plane (Figure 10).

Ground fill is a fairly common technique when laying out PC boards, and one of the main reasons is that it conserves the etching chemicals and/or prevents board warpage. However, for EMC reasons, ground fill is debatable as to usefulness and can actually lead to "high-frequency traces crossing gaps" (Reference 3). In the case where we lack a solid return plane, this issue is compounded by the multiple possible couplings between top and bottom layer routing.

Digital signals are not the result of electron flow through circuit traces but are propagated via electromagnetic waves between the circuit trace and the nearest other metal. Because we lack a solid ground return plane, these EM waves must be "trapped" between two pieces of metal at all times to propagate the signal energy from point A to point B. However, without an adjacent and solid return plane, the signal energy in the EM wave will couple to all other traces they pass by. Please refer to my PC board design series starting with Reference 4.

It's possible to re-lay out this board with the top layer as mainly routed power and signals and then use a semi-solid return plane for the bottom layer with minimal non-critical signal routing. You'd need to be careful to avoid highfrequency traces crossing gaps in this return plane.

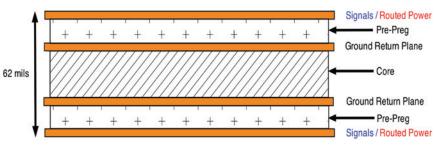

Many of my clients have already invested their design in a two-layer board, only to learn at the last minute that it may never pass EMC requirements. So, often, I'll suggest keeping the current layout but simply adding two additional ground return planes as layers 2 and 3, which should be bonded together (along with all ground fill) with stitching vias in a grid pattern. Today, the cost differential between two- and four-layer boards

is insignificant, so this is often the most cost-effective solution. The suggested stack-up is shown in Figure 11.

#### SUMMARY

In this exercise, I've purposely selected a board design with known design issues to show the basic process I use for characterizing a circuit board using some basic

Figure 10: Here is the PC board layout showing the top (in red) and bottom (in blue) layers. Because there is no solid ground return layer, the fields from the DC-DC converter and 16 MHz clock couple throughout the board.

EMC probes. I suspect that adding the two solid ground return planes would resolve most of the emissions and immunity problems.

There are other design issues that would preclude me from using this particular board in a "real" product. For example, it lacks power input filtering as well as filtering or ESD protection on the I/O pins. I'd also change the I/O connectors to include optional I/O cable shields.

In future articles, we'll be characterizing a more complex embedded computer with USB, Ethernet and HDMI ports, along with multiple DC-DC converters.

#### REFERENCES

- 1. OSEPP Bluetooth module design information

- 2. Wyatt, "Characterize DC-DC converter EMI with nearfield probes," *EDN*.

- 3. Wyatt, "Gaps in return planes yes or no?" EDN.

- 4. Wyatt, "Design PCBs for {low} EMI, Part 1: How signals move," *EDN*.

Figure 11: One possible stack-up suggestion with two added ground return planes that would likely mitigate most all the EMC issues: radiated, conducted and immunity.

#### MILITARY AND AEROSPACE EMC

## Portable Electronics Onboard Aircraft Part 2

#### By Patrick André

n the last blog, we discussed how the FAA and aircraft industry recognized that personal electronic devices, or PEDs, were causing problems aboard aircraft. With the proliferation of PEDs onboard, and especially those with wireless capabilities, action was needed quickly to address safety concerns. The FAA requested the RTCA form a new committee, SC-202, made up of over 100 individuals from the aircraft industry, airlines, computer, medical, telecommunication, and commercial electronics industries, consultants, FAA, and elected officials. The group was formed specifically to address PEDs that had transmitters, cellular technology, wireless radio frequency networks, and the like. These transmitting PEDs are referred to as T-PEDs.

There was a recognition that guidance for the use of T-PEDs was extremely important. Incidents were being reported, often anecdotal and erroneous or misinterpreted. However, it created much interest in the media and the public. Several issues with PEDs were found, including:

- They were not configured the same, or maintained, and thus could be degraded;

- They could be located anywhere in the passenger deck, including (and often) in the flight deck;

- T-PEDs could be activated, deactivated, carried on the person, stowed in luggage, or in a number of other variabilities;

- T-PEDs had less stringent standards applied than aircraft-installed equipment. This resulted in a collision between T-PEDs operating bands and aircraft radio bands.

SC-202 recognized that there was not a well-established understanding of the degree to which aircraft were tolerant of T-PEDs or the importance of each phase of operation (departure and arrival, cruise, taxi, or parked). The issue had to be quickly addressed, which induced performance of tests of the T-PEDs, analysis of the aircraft to be immune, and understanding that would be a monumental task on many aircraft, then to perform testing to determine potential issues. Front-door coupling (direct exposure to the aircraft antenna) and back-door coupling (exposure to the cabling or directly into the equipment) were addressed.

The technology of many aeronautical signals at the time was of 1940s vintage, including VOR, Glideslope, and Localizers used for landing. These did not include advanced signal processing to mitigate interference signals from PEDs or T-PEDs. Receivers that were exposed to out-of-band interference from T-PEDs could become desensitized, losing operational dynamic range. Intermodulation products, cross modulation, spurious emissions, and many other problems were considered. After four revisions were generated in four years, the 2008 edition of DO-294C, Guidance on Allowing Transmitting Portable Electronic Devices (PED) Tolerance, is 412 pages long and provides recommendations on how to deal with these issues.

Understanding this was not adequate, SC-202 also created DO-307, Aircraft Design and Certification for Portable Electronic Devices (PED) Tolerance. Work was continued by SC-234, which updated the document to

DO-307B in 2022. Along with the 2016 document DO-363, Guidance for the Development of Portable Electronic Devices (PED) Tolerance for Civil Aircraft, they provide airframe manufacturers and airlines with methods to determine safety margins and criteria for risk assessment and the ability to analyze, troubleshoot, and mitigate issues that may be found.

Much of the instrumentation testing is based on DO-160D and later. In general, to assure tolerance to T-PEDs. Category R is often the minimum level required for Section 20. Category R has two advantages. First, radiated susceptibility is stepped from 20 V/m below 400 MHz to 150 V/m above, where many of the T-PEDs transmitters operate. It also uses 0.1%-4% pulse modulation instead of squarewave amplitude modulation or 50% duty cycle pulse modulation. This short duration modulation is more in line with the type of transmissions encountered from T-PEDs. In comparison, Category W of 100 V/m starts at 100 MHz and is performed both CW and with 50% squarewave modulation. For many avionics, despite being a lower level above 400 MHz, Category W is a more difficult requirement to meet.

#### PRACTICAL ENGINEERING

## Standards for Electricity Meters and Other Similar Devices

#### By Don MacArthur

E lectricity meters and other similar devices have their own set of unique standards and requirements. The following describes these requirements, the challenges involved, and the status of some requirements.

#### **ELECTRICITY METER NAMES/TYPES**

Electricity meters are sometimes called AC watthour meters, demand meters, power metering and monitoring devices (PMD), power quality meters, and power quality analyzers, to name a few.

#### **METER STANDARDS**

There are both national (ANSI) and international (IEC) standards that cover the various meter names/types. Table 1 is only a partial list of meter requirements.

For meters going to Mexico, Comisión Federal de Electricidad (CFE) standard G0000-48-2010 is required for stand-alone meters. G0000-48-2010 derives its requirements from the IEC meter standards. In 2025, an entirely new standard for meters sold into Mexico will take effect. This standard is NOM-001-CRE and brings with it an entirely new set of requirements for meters and requires meters to have the capability for easy replacement via some type of extractable case.

Meters sold into Australia and New Zealand require certification by the Australian National Measurement Institute in accordance with NMI M6-1, which follows the Australian versions of the LEC meter standards.

IEC 61000-4-30, Power Quality Measurement Methods specifies two different classes of meters, Class A and Class S. Class A and Class S are determined by performing IEC 62586-2:2017, Power quality measurement in power supply systems - Part 2: Functional tests and uncertainty requirements on the meter. Class A pertains to highly accurate meters, whereas Class S is not as rigorous and is applied to less accurate meters.

IEC 61557-12, Performance measuring and monitoring devices (PMD) requires testing to IEC 61326-1 for EMC and IEC 61010-1, IEC 61010-2-030, and IEC 61010-2-201 for product safety.

| ANSI Standard #              | ANSI Description                                                                          | IEC Standard #                        | IEC Description                                                                                                                                                                                                               |

|------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C12.1-2022                   | Electric Meters - Code for<br>Electricity Metering (Replaced<br>C12.1-2014 & C12.20-2015) | IEC 62052-11:2020                     | Electricity metering equipment - General requirements, tests, and test conditions - Part 11: Metering equipment                                                                                                               |

| ANSI C12.10-2011<br>(R2021)  | Physical Aspects of Watthour<br>Meters - Safety Standard                                  | IEC 62053-22:2020                     | Electricity metering equipment - Particular requirements -<br>Part 22: Static meters for AC active energy (classes 0,1S, 0,2S and 0,5S)                                                                                       |

| ANSI C12.18-<br>2006 (R2016) | Protocol Specification for ANSI<br>Type 2 Optical Port                                    | IEC 62053-24:2020                     | Electricity metering equipment - Particular requirements -<br>Part 24: Static meters for fundamental component<br>reactive energy (classes 0,5S, 1S, 1, 2 and 3)                                                              |

| ANSI C12.19-2021             | Utility Industry End Device Data<br>Tables                                                | IEC 61557-12:2018                     | Electrical safety in low voltage distribution systems up<br>to 1000 V AC and 1 500 V DC - Equipment for testing,<br>measuring, or monitoring of protective measures -<br>Part 12: Power metering and monitoring devices (PMD) |

| ANSI C12.21-<br>2006 (R2016) | Protocol Specification<br>for Telephone Modem<br>Communication                            | IEC 62052-31:2015                     | Electricity metering equipment (AC) - General<br>requirements, tests, and test conditions - Part 31: Product<br>safety requirements and tests                                                                                 |

| ANSI C12.22-2012<br>(R2020)  | Protocol Specification<br>for Interfacing to Data<br>Communication Networks               | IEC 61000-<br>4-30:2015<br>+AMD1:2021 | Electromagnetic compatibility (EMC) - Part 4-30:<br>Testing and measurement techniques - Power quality<br>measurement methods                                                                                                 |

ANSI standards are applied to devices sold into the United States, Canada, and some Latin American countries. Entities such as the New York State Department of Public Service Commission require all meters used at their facilities to comply with ANSI standards.

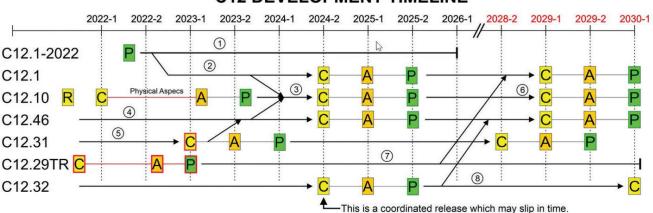

Many of the ANSI meters standards are currently under revision, new standards are in progress, and a few are slated for replacement by newer versions.

- ANSI C12.31-202x establishes standard definitions of AC electrical power (active, reactive, and apparent), AC electrical energy (active, reactive, and apparent), and power factor in terms of sampled voltage and current measurements.

- ANSI C12.32-202x (2nd Edition) covers DC Metering.

- ANSI C12.46-20xx, based on OIML R46:2012 and many IEC standards, is a performance standard for the measurement of active, apparent, and reactive energy that is intended to replace ANSI C12.1.

Image by Pixelharvester from Pixabay

• A new ANSI demand metering standard is also in the work, the number of which has yet to be defined.

The chart in Figure 1 indicates the latest timeline for the release of new ANSI meter standards.

#### CHALLENGES OF MEETING METER STANDARDS

ANSI C12.1 requires that voltage and current inputs to the meter pass a surge test of 6 kV and a 2 Ohm source impedance. This is a much tougher test than what is required by IEC standards.

- ANSI C12.1 requires the meter to pass Class B emissions.

- ANSI and IEC standards are not yet fully aligned, and keeping track of the differences is burdensome.

- ANSI standards are currently in a state of change, and the update process is lengthy.

- Depending on the requirement, meters must maintain accuracy during and after they are subjected to EMC immunity and other environmental influence quantities. **©**

#### C12 DEVELOPMENT TIMELINE

() Keep 2022 version active until other path 1,46, 10 is completed and for a period of overlap.

- ② Split C12.1 into a basic document, move all safety to C12.10, remove performance testing, to be replaced by C12.46

- ③ C12.10 becomes a construction, durability and safety standard

- ④ Continue C12.46 development as a performance only standard. Coordinate with C12.10 and C12.1 so we end up with a base standard, performance standard and safety standard.

- ③ Release C12.31 as soon as possible so necessary tests can be developed and included in C12.46

- Synchronize release of C12.1, C12.10 and C12.46 in new format.

- ⑦ Once C12.29 has sufficient exposure merge it into C12.1 as part of field verification.

- Image: Image:

C Editorially Complete, ready for ballot A Balloted and voted to Accept P Published R Re-affirmed Done

## TACKLING LOW-VOLTAGE SIGNALING IN INVERTER DESIGN: PART 1

Managing High-Power Inverter Noise to Protect Low-Voltage Signals

Christopher Semanson is a System and Solution Engineer at Renasas Electronics America, Inc. in Durham, NC, supporting a wide variety of general-purpose applications dealing with microcontroller unit (MCU), memory protection unit (MPU), and electrical system design. He has previous experience in EMC Education at the University of Michigan, teaching EMC and Electronics with Mark Steffka and in Software Systems and John Deere and Ford Motor Company. Semanson has a bachelor's degree in electrical and computer engineering and a master's degree in electrical engineering from the University of Michigan Dearborn. He can be reached at chris.semanson@renesas.com.

By Christopher James Semanson

Not long ago, the electrification of consumer machinery was primarily limited to hybrid electric vehicles (HEVs), marketed as the next generation of clean propulsion but largely out of reach for the average consumer. Now, with the advent of affordable, high-end microcontroller units (MCUs) and high-efficiency semiconductors, the adaptation of motor control has become more accessible, expanding electrification into secondary markets such as turf care and agricultural equipment, in addition to a growing HEV market. This shift means that embedded system or module development engineers are encountering new challenges associated with electric drives.

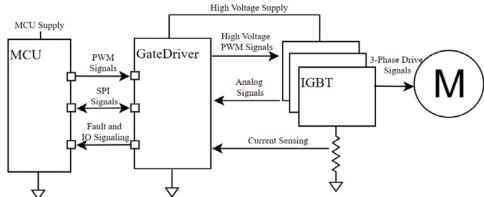

Central to these advanced systems are the power electronic components that constitute the inverter system. These components are responsible for converting DC voltage from a generator or battery

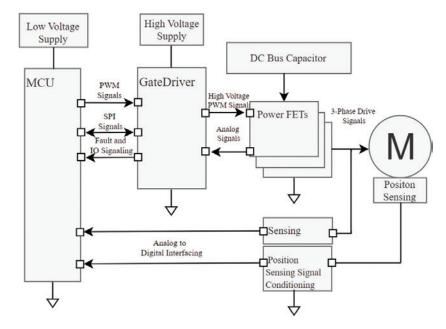

into an appropriate signal to drive a three-phase motor. Designing and interfacing with the control electronics of inverters present unique challenges, particularly in managing signal integrity and mitigating noise. To illustrate these complexities, a typical inverter system is depicted in Figure 1.

A significant challenge in designing and interfacing with electric drives is managing signaling levels and their susceptibility to conducted electrical noise from the inverter's output stage. However, with inverters switching hundreds of amps, the quest for high efficiency, module designers have optimized for minimal dead times, high drive strength, and fast edge rate; all of which come at the expense of electrical noise. These modules typically operate across a wide range of voltages, from 50V to several hundred volts, and at varying power levels tailored to specific applications. However, the signaling voltage levels, constrained by the process technology, generally range from 1.8V to 5.0V.

Balancing the need for the highest efficiency with typical voltage input output ( $V_{IO}$ ) levels and ensuring that the controller can accurately manage the drive becomes a primary challenge for both embedded and analog engineers.

To better understand the challenges involved in designing, building, and debugging a high-power mixed-signal inverter, Part 1 of this two-part article will provide an in-depth discussion of the components and functions of an inverter. This includes examining

Figure 1: Example diagram of a typical inverter system

common application-specific integrated circuits (ASICs) that work alongside field effect transistors (FETs) and MCUs, focusing on their roles in interfacing and driving. We'll also address common functions such as communication and GPIO (general purpose input output) usage.

## IDENTIFYING COMMON LOW VOLTAGE SIGNALING INTERFACES

Interfacing between the MCU and external ASIC circuitry as sensitive traces is the first step in mitigating noise since each interface plays a specific role in the command and control of the module at the application layer. To better understand their functions and potential failure modes, the low voltage interfacing is categorized into the following groups of GPIO:

- Inter-integrated circuit communication interface (I<sup>2</sup>C)/serial peripheral interface (SPI) communication lines—These are the most common types of communication interfaces, especially for advanced ASICs such as smart gate drive devices and external monitor circuitry. I<sup>2</sup>C operates with an open-drain configuration, while SPI uses a push-pull mechanism.

- *Low voltage drive signals*—These signals are used for the command and control of drivers, typically driven by a timer circuit. They generally interface with a level shifter or gate driver that controls the motor.

• *Critical GPIO signals*—These include fault processing signals used to quickly disable the drive, reset pins to alert the MCU of issues in the drive circuitry, and control pins for the ASIC's functionality. Although less common, these signals are needed to obtain real time operational fault and drive status while under operation.

In any of the above scenarios, incorrect signal detection due to coupled noise from the power FETs can lead to challenges specific to that signal's function. What makes these signals sensitive is the small signal-to-noise ratio they have, inherent in many ASICs and MCU interfacing structures. This vulnerability arises because ASICs tend to operate with low IO voltage ( $V_{IO}$ ), typically on a CMOS level from either:

- External V<sub>IO</sub>—Interfaces with the MCU, allowing the ASIC to signal at voltages as low as 1.8 V; or

- Internal V<sub>10</sub>—Logic levels designed around a 3.3V internal reference, a typical CMOS signaling level.

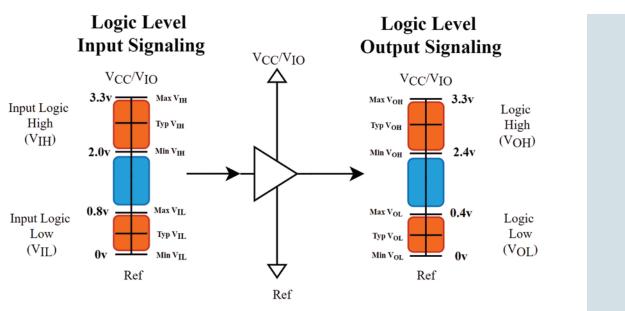

The <u>noise</u> generated by high-power switching transients is often comparable to these low signal levels. A transient that crosses the threshold for a long enough time (i.e., exceeds a deglitch time, or  $T_d$ ) to trigger a logic switch results in incorrect actuation. To better understand how high levels of transients can affect IO signaling, it is essential to refer to the datasheet where the input high ( $V_{II}$ ) and low ( $V_{II}$ ) levels are defined.

Figure 2:  $V_{\mu}/V_{\mu}$  signaling levels for an input buffer

#### EXAMINING V<sub>IH</sub>, V<sub>II</sub> FROM THE DATASHEET

When designing a signaling interface to an ASIC, engineers should first consult the datasheet for minimum, typical, and maximum values. These datasheet values are tested at manufacturing, and the ASIC manufacturer strives to not ship pieces that operate beyond these limits. The values define your operating parameters and edge cases where you want to stay away from:

- *V*<sub>*IH*</sub>—The voltage at which the input triggers a low-to-high transition;

- $V_{IL}$ —The voltage at which the input triggers a high-to-low transition; and

- *Minimum pulse width, debounce, or deglitch time* The minimum time a signal must persist above or below the voltage thresholds for a logic level threshold change.

Figure 2 illustrates typical 3.3v CMOS TTL gatelevel input and output signaling.

To assess how these logic levels impact noise tolerance, we must first investigate the structure of an input buffer representative of a standard CMOS input to an ASIC.

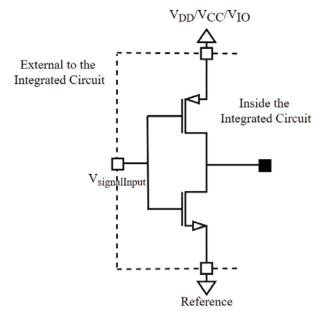

The model shown in Figure 3 depicts an input logic circuit referenced to a  $V_{IO}$ , primarily at DC. At the top of the input, we generally find  $V_{IO}$  or a

reference voltage, either externally fed or internally generated. The key voltage levels are when the inverter circuit recognizes a logic high, with added hysteresis, and when it recognizes a logic low, again with hysteresis. When transient characteristics are introduced, trace parasitic can significantly impact circuit performance during coupled switching transients on the reference, power, or input lines.

Figure 3: Example of a buffer circuit inside the ASIC

## New Application Note: The Fundamentals of EMC

| Fundamentals of<br>Electromagnetic Compliance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Coilcraft                                                                                                                                                      |               | 1.11000-010 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|

| Heradelini<br>Reson y can an angue of adverse from<br>the adverse of the second second second<br>adverse of the second second second<br>second second second second second<br>second second second second second<br>second second second second second second second<br>second second second second second second second second second second<br>second second sec | <text><section-header><section-header><section-header><section-header><text></text></section-header></section-header></section-header></section-header></text> | <text></text> |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | descention interesting                                                                                                                                         |               |             |

- Reviews sources of electromagnetic noise and modes of noise propagation

- Lists EMC compliance agencies and testing standards

- Provides design hints for passing EMC pre-compliance and compliance tests

Learn more @ coilcraft.com/AppNotes

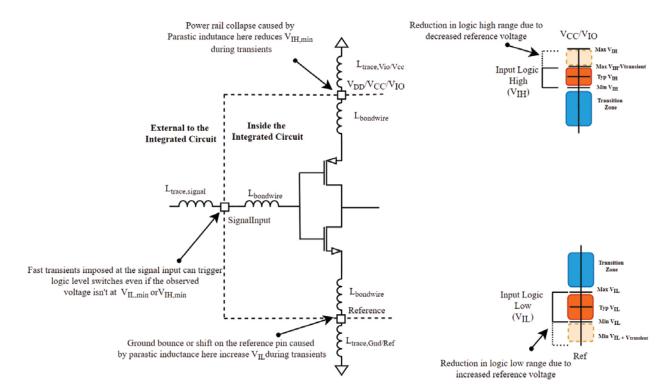

Figure 4: The previous circuit structure with labeled parasitic and its impact on  $V_{\mu}$  and  $V_{\mu}$  levels

Additionally, the voltage levels defined in datasheets are typically guaranteed at DC, determined by slowly ramping a voltage signal up and down to obtain minimum, typical, and maximum values. If we apply a switching transient coupled onto either the inverter input, power, or ground, ringing can:

- Collapse the power supply momentarily reducing your V<sub>IH</sub> levels;

- Bounce the reference (or ground) momentarily impacting V<sub>IL</sub> levels; MCU Sup

or

Couple onto your input signal, causing an incorrect V<sub>IH</sub> to be detected, or even worse, cause overshoot that the typical oscilloscope is not able to detect.

Figure 5: A simplified inverter system with gate drive

The impact of the transient's scale with the speed and power of the switching signal. So the faster the transient, the more impact in terms of coupling, reference bounce, or power rail collapse.

After understanding how reducing  $V_{\rm CC}$  or increasing the reference to your circuit can impact  $V_{\rm IH}$  and  $V_{\rm IL}$  values, the discussion can shift to how this noise impacts gate drive, I<sup>2</sup>C/SPI, and other GPIO signals that operate at CMOS levels.

#### **IMPACT OF NOISE ON GATE DRIVE ASICS**

The control strategy behind an inverter and how it creates AC power from DC is complex enough to fill a book. However, at its most basic level, the motor is controlled by filtering tightly controlled pulses through motor windings to create AC currents. Since the MCU isn't capable of driving the output switches directly, a level shifter or a more commonly found gate drive ASIC is used (often labeled a "Smart" Gate Driver). A simplified diagram is depicted in Figure 5.

Applications that rely on gate drive ASIC performance generally employ features such as:

- *Monitoring the voltage and currents across the FETs* Ensuring that parameters are within safe operating ranges and provides protection when they're not.

- *Automatic deadtime insertion*—Preventing shootthrough by inserting a delay between turning off one transistor and turning on the complementary transistor.

- *PWM mode selection*—Allowing the selection between 3 PWM (where opposite side drives are complementary, controlled by the gate driver circuit with trimmable deadtime insertion) or 6 PWM mode (where all low side PWM drive pulses are controlled by the MCU).

Despite the advanced functionality of the gate drive ASIC, it ultimately reacts to the low voltage side inputs. This means that if transient spikes on the input persist above the  $V_{IH}$  for longer than  $T_d$ , it will pass that pulse through to the high side of the gate driver. As a result, noise coupled onto the low voltage side of the device can manifest itself in several ways depending on how and where the noise is imposed onto the device IO.

If the noise voltage couples onto the low side PWM signals, it runs the risk of actuating the high side and low side at the same time. This could result in shoot through or shoot through protection, which occurs when both transistors conduct simultaneously, resulting in a temporary short circuit.

Gate drivers often include protection logic to prevent this, along with modification of deadtime to better control switching performance. The high-side and low-side gate pulses control the switching of

#### Superior Products, Outstanding Service

## WE SPECIALIZE IN DOORS

We manufacture custom, durable and low-maintenance doors that deliver highly effective shielding and smooth operation.

- High Traffic Bladder Doors

- Sliding Doors

- 2 Double Doors

- Single Doors

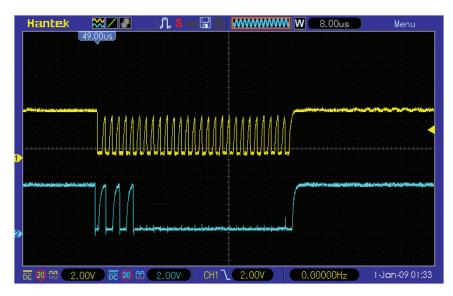

Figure 6: (Left) Noise on the AGND reference net that should be 0v, (Right) gate pulses, the cause of the reference noise

transistors that drive the e-machine and are generally complimentary to each other in 3-pwm mode, and in 6-pwm mode they are driven complimentary. Gate drive ASICs have functions and characteristics that manage these by automatically protecting the switches from short circuiting as well as automatic dead time insertion, along with calibratable drive strength.

The most common type of shoot through protection that ASICs employ is automatic early pulse termination. This, erroneously, happens either:

When bounce on the reference plane from opposite side switching pulse either lifts the reference high enough to trigger the opposite side, or creates a noise voltage spike, causing an early termination of the driving pulse; or

• When a voltage transient larger than the VIH threshold is detected at the input of the low voltage side. These transients are generally very difficult to measure accurately due to the parasitic of the probe and probe clip being able to be easily loaded. As such, they are generally estimated from a measurement of the ground or by overlaying a switching pulse.

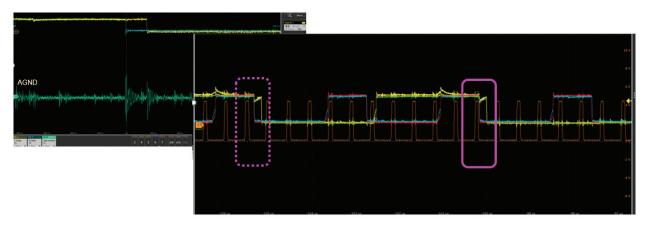

Examples of a reference bouncing are shown in Figure 6.

In both pictures, the magnitude of the noise on the "AGND" net causes the reference to move, caused by the orange PWM signals on the picture to the right. When lined up properly, as outlined in the solid pink box, this can cause incorrect actuation of the neighboring low voltage signal in either incorrect triggering or a missed trigger.

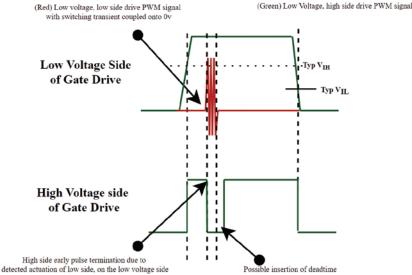

This interaction leads to the diagram below depicting early pulse termination and its impact on the high voltage drive pulse. As the diagram in Figure 7 shows, the moment the noise voltage crosses the  $V_{\rm IH}$  threshold, the pulse is terminated, deadtime is inserted, and the pulse is driven low, only to be driven

Figure 7: Example of early pulse termination due to the gate driver trying to prevent simultaneous high/low side actuation

Quality & Service for EMC

Professional EMC Testing Solution Provider

high again when the transient event is over, causing erratic motor operation.

In the event the gate driver ASIC does not have active protection, designers generally rely on complimentary parts of a circuit to drive the output in 3-pwm mode, where the low side turns on when the high side turns off. However, the issue still remains and is compounded because, while the pulses are complimentary of each other, they are still subject to trace capacitance, which can impact the propagation delay of the complimentary signal, which could cause accidental shoot through.

Next, we'll focus on the impact of noise on I<sup>2</sup>C and SPI communication buses.

#### IMPACT OF NOISE ON COMMON COMMUNICATION INTERFACES

While incorrect actuation on IO and drive signals is relatively easy to visualize, their impact on standard communication interfaces like I<sup>2</sup>C and SPI is more subtle and can create difficult-to-debug challenges. To better identify these issues, let's briefly overview the interfaces:

- *I*<sup>2</sup>*C*—I<sup>2</sup>*C* is a common hardware interface and protocol used to facilitate communication between ASICs and a controller MCU. The hardware is designed as an open-drain, pulldown circuit, which requires pullup resistors to the IO voltage level. Its idle state is typically pulled high, and it counts nine clock edges per 8 bits of data transferred. I<sup>2</sup>*C* uses two wires: a clock line and a data line, connecting the controller to its peripherals.

- *SPI* SPI is a common hardware-defined interface that functions as a shift register between the controller and peripherals. The hardware operates much faster than I<sup>2</sup>C, as it is a driven interface (commonly referred to as push-pull). SPI typically uses four wires: clock, data in, data out, and chip select.

The digital block in both of these communication interfaces typically features a state machine that counts edges when they receive the signal to begin a frame. The clock is specifically controlled by the controller in typical situations. If incorrect actuation occurs due to a high-power transient coupling onto In Compliance with MIL - STD - 704 HB 20326.1 - 8

## PPS 45C10 🐨

#### Aircraft AC / DC Power Characteristics Test System

- Max. AC voltage 450 Vrms, 105 Arms (1 phase), 35 Arms (3 phase)

- > Max. DC voltage ±636 Vrms, ±105 Arms

- > Output Power 20 kW

- > Support 3 phase / single phase / split phase output

- > Built-in arbitrary wave generator

- Ethernet RJ45 interface for software remote control

- > Frequency DC-200 kHz

- > Support harmonics output

- > Support frequency/amplitude modulation

- > Simulate complex waveform

- > Support ripple closed loop tests

- Four quadrant power supply, can be used as a load

#### SUZHOU 3CTEST ELECTRONIC CO., LTD.

Add: No.99 E'meishan Road, SND, Suzhou, Jiangsu Province, China Email: globalsales@3ctest.cn Ph: + 86 512 6807 7192 Web: www.3c-test.com

either the clock or data lines, we risk encountering the following challenges:

- *Data corruption:* When pulses on the data line aren't read properly by the controller, data validation can be performed via CRC. If the CRC does not match, the frame is dropped. This method applies to both I<sup>2</sup>C and SPI.

- *Clock corruption:* Clock corruption is more nuanced and depends on which part of the communication interface is impacted.

- *Near-end crosstalk:* Noise coupled onto the clock signal near the controller can cause the controller to count extra clock pulses. This could lead to early termination or releasing of the bus while the peripheral device is still transmitting, leading to a stuck bus condition.

- *Far-end crosstalk:* Noise coupled onto the clock signal near the peripheral device can cause the peripheral to count extra clock pulses. This could result in incorrect data being sent, or an error in communication between the peripheral and controller devices.

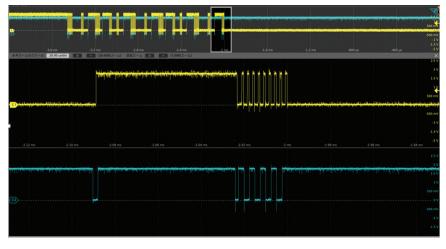

In all of these situations, the impact is again difficult to measure due to probe parasitic. In Figure 8, we can see what appears to be a good I<sup>2</sup>C transaction, but the result is a stuck bus line.

This situation resulted in the controller or peripheral clock counters becoming out of sync, incorrectly missing a clock pulse, even though an oscilloscope demonstrates otherwise. On a communication bus, this desynchronization can lead to a bus-stuck condition, where a device holds down either the clock or data, waiting for extra edges that will never come. Each situation requires software intervention to recognize the issue and release the bus.

Additionally, because each interface is controlled in a different circuit manner, they're impacted differently. Since I<sup>2</sup>C is an open-drain interface, it is primarily impacted by reference bounce and *pullup strength*, especially during transitions. The pulldown is expected to be referenced to the same 0 V at both the near and far ends.

Figure 8: Example of an oscilloscope detected a proper I<sup>2</sup>C transaction, but the bus is held due to the ASIC not detecting the pulsetrying to prevent simultaneous high/low side actuation

Figure 9: Example of a I<sup>2</sup>C transaction with a very weak pullup, clock glitching, and narrow duty cycle still being detected properlytransaction, but the bus is held due to the ASIC not detecting the pulsetrying to prevent simultaneous high/low side actuation

And while I<sup>2</sup>C is tolerant to a wide variety of pullup and duty cycle conditions, as shown in Figure 9, it is important to choose the right operating conditions. the correct PCB stack up during component selection and placement, including placeholders for components that otherwise can be unpopulated. **(**)

As SPI is a push-pull interface, its impact is limited

to glitches on either the clock or data lines during transmission, and typical errors here are in extra clock pulses inserted on the SCK (resulting in a stuck bus) or extra data pulses on either the serial out or serial in data lines (resulting in a corrupted packet).

While coupled transients can significantly affect GPIO drive signals and the communication interface to typical ASICs, we can now explore techniques and complementary circuits that can be implemented to mitigate these issues. In many situations, conducted electrical noise is inherent to the design of high-power inverter systems. Mitigation strategies can be divided into two main categories:

- Components used for impacting the sharp edges that are the source of electromagnetic interference; and

- Layout and planning to ensure that the system has the best chance of avoiding issues by placing connectors and creating a stack up that shield low voltage circuitry.

#### CONCLUSION

With the push across various industries to hybridize machines that would otherwise be pneumatic or hydraulically driven, inverters are becoming prolific. The design challenges that come along with these inverters are often centered around the balancing of being robust to high voltage transients on low voltage signaling and switching efficiency in order to get the most out of the inverter. In Part 2 of this article, we'll discuss the importance of choosing

- VSWR reflected power protection

- Plug and play field replaceable power supplies

- And more...

CPI Electron Device Business' solid-state and TWT amplifiers operate in the range DC-40 GHz up to 50 kW pulsed and CW.

Delivering the highest field strengths in the test environment, they meet the most demanding worldwide testing standards; including RTCA/DO-160, MIL Standard, EUROCAE and AIRBUS ABD 100.

They are based on the same switched mode power supply technology as the rugged amplifiers with all the advantages of performance and reliability that entails, but neatly re-packaged into compact, lightweight and affordable rack-mountable units.

For more information on the range of instrumentation amplifiers, or to find out about other bespoke solutions, email us at <a href="mailto:ElectronDevices@cpi-edb.com">ElectronDevices@cpi-edb.com</a> or visit our website.

## CURRENT PROBE SPECIFICATIONS AND THEIR IMPACT ON CONDUCTED EMISSIONS MEASUREMENTS

Addressing the Limits of CISPR 25 Measurement Methods

urrent probes are used to perform conducted emission (CE) measurements in accordance with various product standards like CISPR 11, CISPR 25, or CISPR 32. All these product standards refer to the basic standard CISPR 16-1-2 (2014), which includes normative specifications for current probes in clause 5.1.3. Some of the current specifications include:

- *Insertion impedance:* 1  $\Omega$  impedance maximum;

- Transfer impedance: 0.1 Ω to 5 Ω in the flat linear range; 0.001 Ω to 0.1 Ω below the flat linear range (current probe terminated into 50 Ω load);

- *Added shunt capacitance:* less than 25 pF between the current probe housing and measured conductor; and

• *Frequency response:* Transfer impedance is measured over a specified frequency range to calibrate the probe; the range of individual probes is typically 10 kHz to 100 MHz, 100 MHz to 300 MHz, and 200 MHz to 1,000 MHz.

In the recent past, questions have been raised about the usefulness and appropriateness of these specifications and how commercially available and widely used current probes meet these specifications over required frequency ranges. These concerns have been formally documented, for example, in a document issued in April 2023 by CISPR/D, the subcommittee responsible for CISPR 25.

Furthermore, work related to the definition and measurement methods for the specification "insertion

Bruce Harlacher is Vice President of Engineering at Fischer Custom Communications, where he supports product development and applications. He has 50 years of experience in RF test instrumentation and measurement. Harlacher can be reached at bharlacher@fischercc.com.

Werner Schaefer has 40 years of experience RF/uwave and EMC testing and was involved in the development, marketing, and support of EMC test equipment. He owns Schaefer Associates, a company that provides assessment, training, and consultancy services to the fields of EMC, RF/uwave, and Quality Assurance. Schaefer can be reached at wernerschaefer@comcast.net.

#### By Bruce Harlacher and Werner Schaefer

impedance" was initiated by CISPR/A/WG1 in 2017 to address the current lack of a standardized measurement method.

This article will discuss the following aspects related to the above CISPR 16-1-2 requirements, including:

- The appropriateness of the 1 Ω Insertion Impedance specification in the context of its impact on both the calibration process and for measurements using a simple CE test configuration, per CISPR 25 (see Reference 1);

- Meaning and usefulness of the shunt capacitance specification; and

- Practical purpose and usefulness of various inferred "limits" for current probe transfer impedance versus frequency, as documented in Reference 5.

#### **CURRENT SITUATION**

The CISPR 16-1-2 requirements cited in the introduction were originally included in CISPR 16-1 before 1999 and were transferred to CISPR 16-1-2 with no changes since then. No information is available in the CISPR 16 set of documents (e.g., CISPR 16-3) regarding the assumptions made for establishing current specifications as far as their values and associated frequency ranges are concerned. However, since these specifications are placed in the normative part of the standard, they are to be interpreted as normative requirements that current probes must meet in order to be used in measurements in accordance with product standards (e.g., CISPR 25).

The situation is compounded by the fact that for some specifications no definition for "insertion impedance" exists, and no agreed-on measurement methods are made available to determine the values of specifications like insertion impedance or "shunt capacitance." Additionally, there is a misalignment between CISPR 16-2-1 and product standards regarding the frequency range for specifications. Most product standards use the current probe in the frequency range of 150 kHz to 30 MHz for conducted emission measurements, with the exception of CISPR 25, which calls out a maximum frequency of 245 MHz for current probe measurements. CISPR 16-1-2, on the other hand, defines several frequency ranges for the specification of frequency response, up to 1 GHz.

This situation has created considerable confusion among users as to how rigorously to apply the current probe requirements in CISPR 16-1-2 when purchasing current probes or calibration services for current probes. Some concerns were formally raised by some CISPR product committees like CISPR/D and CISPR/A that started the process to formally address these concerns. Several aspects are currently under discussion and the three topics previously outlined do serve as input to the resolution of currently existing problems related to current probe specifications.

#### INSERTION IMPEDANCE MEASUREMENT DISCUSSION

In CISPR/A, three different methods to measure the insertion impedance of current probes were proposed in 2018. However, these methods only cover the frequency range of up to 30 MHz, which excludes a large portion of the frequency range stipulated by CISPR 25 (up to 245 MHz). The rationale for the limitation of the frequency range to 30 MHz was given as the requirement for the calibration fixture dimensions needing to be small compared to the wavelength. This explanation is not obvious since the wavelength at 30 MHz is 10 m, and all calibration fixtures have dimensions that are more than an order of magnitude smaller for the current probes used for conducted emission measurements in accordance with CISPR product standards.

The three proposed measurement methods introduced by CISPR/A Working Group 1 are addressed in the following sections.

#### **One-Port Reflection Method**

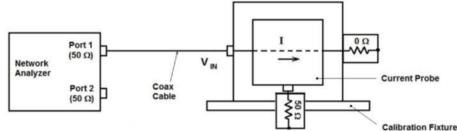

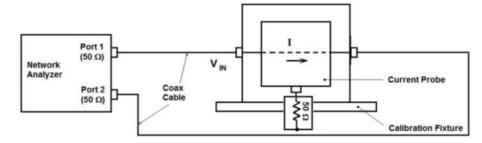

The measurement setup for this method is shown in Figure 1.

While the suggested principle is plausible, it is unclear why the output of the fixture is terminated in a short and not in 50  $\Omega$ . In case of a short, the network analyzer measures a very high reflection in case of an empty fixture and with the probe placed inside the fixture. It seems preferable to measure close to the system impedance of 50  $\Omega$  since the uncertainty contribution of the network analyzer is minimized in this scenario, which improves the uncertainty of the insertion impedance measurement. T-connector somehow included in the network analyzer calibration process? It seems that this method yields a larger measurement uncertainty since the T-connector can cause coupling of the source signal (Port 1) directly to the measurement channel (Port 2), and the reflected signal from the short termination can reflect back into the source channel. As stated in the document, the influence of the calibration fixture on measurement results was unknown, which seems problematic since no details of the fixture were provided in the contribution.

Further work in CISPR/A Working Group 1, completed in 2021, expands on the initial work regarding measurement methods for insertion impedance. The originally proposed measurement methods were repeated, using a calibration fixture

#### Series-Thru Method

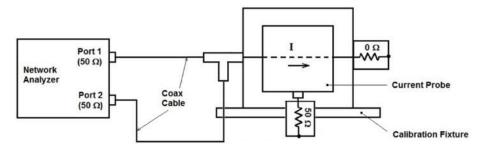

The measurement setup for this method is shown in Figure 2.

This method seems to be more beneficial compared to the one-port reflection method since the system impedance of 50  $\Omega$  is maintained throughout the measurement process.

#### Shunt-Thru Method

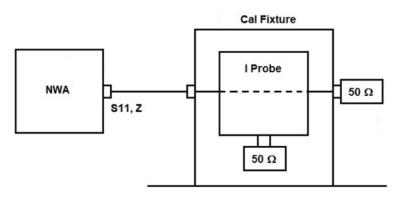

The measurement setup for this method, as described in Reference 3, is shown in Figure 3.

In the description previously provided, it was unclear where the full two-port calibration of the network analyzer is performed. Is the reference plane for the measurement established at the end of the cables without considering the T-connector, or is the

Figure 1: One-port reflection method

Figure 2: Series-Thru method

Figure 3: Shunt-Thru method

suggested by the current probe manufacturer for the probe under investigation. Based on the calculated measurement uncertainty associated with each method, the "shunt-thru method," using a transmission measurement, was identified as the most accurate method to determine insertion impedance. It is to be noted that the measurement uncertainty was only based on the contribution of the network analyzer, not considering possible fixture influences. It would be beneficial to investigate the influences by using different fixtures to be able to determine the impact on the insertion impedance measurements.

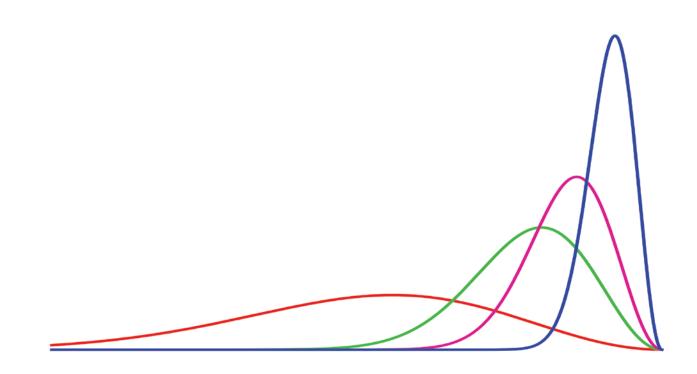

While the "shunt-thru method" to 30 MHz looks like the most promising method from a consistency and uncertainty standpoint, the results, presented up to 100 MHz, indicate two things of interest:

- First, the measured insertion impedance is about 3  $\Omega$  and rises with increasing frequency, which does not comply with the current specification; and

- · Second, the measured insertion impedance appears to begin diverging between S11,22 and  $S_{21,12}$  at 30 MHz. This appears to illustrate the difficulty that will be encountered at frequencies above 100 MHz and most certainly at 1 GHz. The divergence shown in the resultant plot infers a fundamental problem in defining the "proper" method, particularly in light of the maximum test frequency range used by CISPR 25.

In CISPR/A, further work was completed in the form of a round-robin test (RRT) to determine the suitability of the "shunt-thru" method based on transmission measurements to 100 MHz to determine the insertion impedance of a current probe. That effort produced the following observations:

- A variety of calibration fixtures were used by participants of the RRT. Only one participant used the calibration fixture suggested by the manufacturer of the current probe.

- On the one hand, this would seem to violate a round-robin concept of all participants using the same hardware (not considering the probe electronics) to isolate differences in how various laboratories execute a given test method. On the other hand, it points out the importance of using a proper test fixture (recommended by the probe manufacturer).

### **ON-DEMAND EMC TESTING CHAMBERS** TO MEET YOUR MOST SPECIFIC NEEDS

EMC Test Chambers

EMC Antennas

- EMC Accessories

- Shielded Doors RF Shielded Rooms

Learn more at: www.mvg-world.com/emc Contact: www.mvg-world.com/en/contact

The RRT summary report acknowledges the fixture issue as the "dominating influence above 600 kHz" and reinforces the notion that the use of the proper calibration fixture is crucial. Furthermore, one conclusion drawn in this paper states that "the measurement method is effective to measure Insertion Impedance of current probes." It is unclear how this general conclusion can be drawn since the measurements were made only up to 100 MHz, not covering the full frequency range to 245 MHz in CISPR 25. In addition, as stated before, the fixture has a significant impact. Therefore, the suitability of the method is dependent on the use of a "proper" fixture.

#### INSERTION IMPEDANCE MEASUREMENT METHOD

Our co-author Bruce's company (Fischer Custom Communications) developed the insertion impedance measurement method prior to CISPR/A's work referenced in this article to better understand insertion impedance. This effort was driven by increasing customer queries involved with measurements in accordance with CISPR 25. The selected insertion impedance measurement approach is very similar to existing calibration protocols and is based on the idea of working in a 50  $\Omega$  system.

Since the insertion impedance discussion tends to be more focused on the calibration aspect, our technical experts elected to focus initially on the calibration perspective, which is discussed later in this article.

Figure 4 shows the basic test setup we used for our insertion impedance investigations, which includes the following steps:

- An S<sub>11</sub> calibration was performed with short, open load at the end of the measurement cable with the network analyzer configured to measure impedance Z based on S<sub>11</sub>.

- 2. The current probe was removed from the calibration fixture;

- 3. A network analyzer sweep was performed and saved;

- 4. The current probe was installed in the calibration, and another network analyzer sweep was performed and saved; and

5. The difference between the two network analyzer sweeps was calculated as the measured insertion impedance.

Early in our research of insertion impedance measurement methods, we recognized the potential for the current probe case to be an influence at higher frequencies. Although not extensively researched, it appeared that the probe case effect was not routinely addressed in the literature. CISPR 16-1-2 specifications treat the case impact as a limit: "Added shunt capacitance less than 25 pF between the current probe housing and measured conductor." Currently, there is no guidance in the CISPR documentation on how to measure shunt capacitance, nor is it clear if this requirement applies to an actual measurement application, a calibration scenario, or both.

References 3 and 4 seem to be typical attempts to model current probes. The primary focus is on the equivalent electrical circuit comprised of the electronics of a current probe. The probe case is not included in the modeling. The previously described measurement treated the probe electronics and its case as an integrated item. With the probe case being a major point of interest, we performed a variety of insertion impedance measurements with and without the use of an empty probe case in an attempt to remove the case influence on the measured insertion impedance.

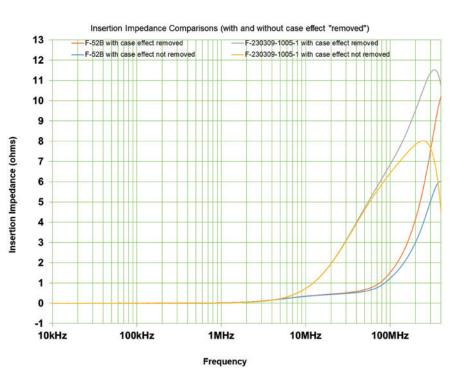

Both types of insertion impedance measurements were made on two different probes. The first is a widely used current probe that has a nominal transfer impedance of about +13 dB ohms from about 5 MHz to 400 MHz. The second probe was one that has a nominal transfer impedance > =20 dB $\Omega$  from about 50 MHz to 1000 MHz.

Figure 4: Insertion impedance method

Many of the experiments we performed measuring insertion impedance with and without case effect removal indicated a complex interaction, likely involving inherent transfer impedance, size of probe case, and maximum frequency of interest.

The results are presented in Figure 5 for both probes and both types of insertion impedance methods previously discussed.

Many of the experiments we performed measuring insertion impedance with and without case effect removal indicated a complex interaction, likely involving:

- Inherent transfer impedance;

- · Size of probe case; and

- Maximum frequency of interest.

These factors seem to add to the difficulty of identifying the "proper" insertion impedance test method.

#### POSSIBLE IMPACT OF INSERTION IMPEDANCE IN A TEST SETUP

The inference of the CISPR 16-1-2 requirement that insertion impedance by less than 1  $\Omega$  at all frequencies (possibly to 1 GHz) is that any value above 1  $\Omega$  might adversely affect the actual conducted emission (CE) measurements. The origin and basis for this requirement is unknown but would seem to be extremely conservative from an application standpoint.

From Figure 13 in CISPR 25 (2021), it is apparent that a loop is formed by the equipment under test (EUT), the load simulator, the interconnecting wire, and the ground plane. It is not clear if the two artificial networks and the DC power supply are part of this loop or if the load simulator provides some electrical isolation between the EUT and power and artificial networks.

Reference 5 investigates the "influence of termination impedance on conducted emissions in automotive high voltage networks." In this document, the authors started with an equivalent circuit that consisted of a loop formed by the DC power (+) side, through a line impedance stabilization network (LISN), through the EUT, and then back to the DC power (-) side after passing through a second LISN.